SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

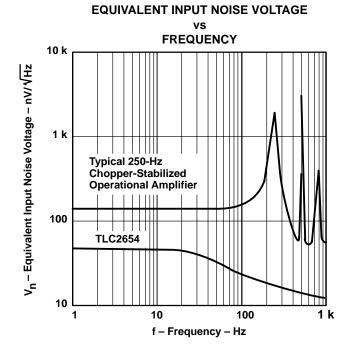

- **Input Noise Voltage**

- 0.5  $\mu$ V (Peak-to-Peak) Typ, f = 0 to 1 Hz 1.5  $\mu$ V (Peak-to-Peak) Typ, f = 0 to 10 Hz 47 nV/ $\sqrt{\text{Hz}}$  Typ, f = 10 Hz

- 13 nV/ $\sqrt{\text{Hz}}$  Typ, f = 1 kHz

- High Chopping Frequency . . . 10 kHz Typ

- No Clock Noise Below 10 kHz

- No Intermodulation Error Below 5 kHz

- **Low Input Offset Voltage** 10 μV Max (TLC2654A)

- **Excellent Offset Voltage Stability** With Temperature . . . 0.05  $\mu$ V/°C Max

- AVD . . . 135 dB Min (TLC2654A)

- CMRR . . . 110 dB Min (TLC2654A)

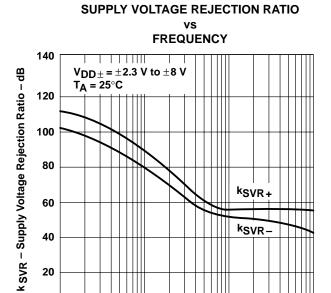

- k<sub>SVR</sub> . . . 110 dB Min

- Single-Supply Operation

- **Common-Mode Input Voltage Range** Includes the Negative Rail

- No Noise Degradation With External Capacitors Connected to V<sub>DD</sub>\_

- **Available in Q-Temp Automotive HighRel Automotive Applications** Configuration Control/Print Support Qualification to Automotive Standards

## description

The TLC2654 and TLC2654A are low-noise chopper-stabilized operational amplifiers using the Advanced LinCMOS™ process. Combining this process with chopper-stabilization circuitry makes excellent dc precision possible. In addition, circuit techniques are added that give the TLC2654 and TLC2654A superior noise performance.

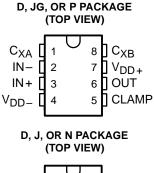

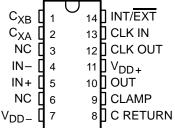

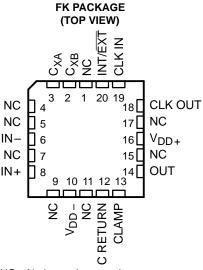

NC - No internal connection

Chopper-stabilization techniques provide for extremely high dc precision by continuously nulling input offset voltage even during variations in temperature, time, common-mode voltage, and power-supply voltage. The high chopping frequency of the TLC2654 and TLC2654A (see Figure 1) provides excellent noise performance in a frequency spectrum from near dc to 10 kHz. In addition, intermodulation or aliasing error is eliminated from frequencies up to 5 kHz.

This high dc precision and low noise, coupled with the extremely high input impedance of the CMOS input stage, makes the TLC2654 and TLC2654A ideal choices for a broad range of applications such as low-level. low-frequency thermocouple amplifiers and strain gauges and wide-bandwidth and subsonic circuits. For applications requiring even greater dc precision, use the TLC2652 or TLC2652A devices, which have a chopping frequency of 450 Hz.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Advanced LinCMOS is a trademark of Texas Instruments

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## description (continued)

The TLC2654 and TLC2654A common-mode input voltage range includes the negative rail, thereby providing superior performance in either single-supply or split-supply applications, even at power supply voltage levels as low as  $\pm 2.3$  V.

Two external capacitors are required to operate the device; however, the on-chip chopper-control circuitry is transparent to the user. On devices in the 14-pin and 20-pin packages, the control circuitry is accessible, allowing the user the option of controlling the clock frequency with an external frequency source. In addition, the clock threshold of the TLC2554 and TLC2654A requires no level shifting when used in the single-supply configuration with a normal CMOS or TTL clock input.

Innovative circuit techniques used on the TLC2654 and TLC2654A allow exceptionally fast overload recovery time. An output clamp pin is available to reduce the recovery time even further.

The device inputs and outputs are designed to withstand -100-mA surge currents without

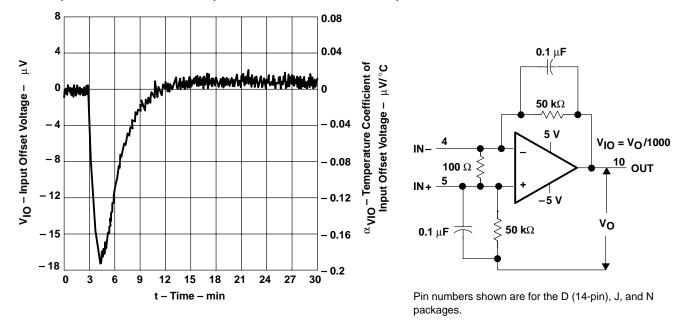

Figure 1

sustaining latch-up. In addition, the TLC2654 and TLC2654A incorporate internal ESD-protection circuits that prevent functional failures at voltages up to 2000 V as tested under MIL-STD-883C, Method 3015; however, exercise care in handling these devices, as exposure to ESD may result in degradation of the device parametric performance.

The C-suffix devices are characterized for operation from 0°C to 70°C. The I-suffix devices are characterized for operation from -40°C to 85°C. The Q-suffix devices are characterized for operation from -40°C to 125°C. The M-suffix devices are characterized for operation over the full military temperature range of –55°C to125°C.

#### **AVAILABLE OPTIONS**

|                |                     |                             |                           | P/                      | ACKAGED DEVICES               | S                       |                         |                           |

|----------------|---------------------|-----------------------------|---------------------------|-------------------------|-------------------------------|-------------------------|-------------------------|---------------------------|

| _              | V <sub>IO</sub> max |                             | 8 PIN                     |                         |                               | 14 PIN                  |                         | 20 PIN                    |

| T <sub>A</sub> | AT 25°C             | SMALL<br>OUTLINE<br>(D)     | CERAMIC<br>DIP<br>(JG)    | PLASTIC<br>DIP<br>(P)   | SMALL<br>OUTLINE<br>(D)       | CERAMIC<br>DIP<br>(J)   | PLASTIC<br>DIP<br>(N)   | CERAMIC<br>DIP<br>(FK)    |

| 0°C to 70°C    | 10 μV<br>20 mV      | TLC2654AC-8D<br>TLC2654C-8D |                           | TLC2654ACP<br>TLC2654CP | TLC2654AC-14D<br>TLC2654C-14D |                         | TLC2654ACN<br>TLC2654CN | _<br>_                    |

| -40°C to 85°C  | 10 μV<br>20 μV      | TLC2654AI-8D<br>TLC2654I-8D |                           | TLC2654AIP<br>TLC2654IP | TLC2654AI-14D<br>TLC2654I-14D |                         | TLC2654AIN<br>TLC2654IN | _<br>_                    |

| -40°C to 125°C | 10 μV<br>20 μV      | TLC2654AQ-8D<br>TLC2654Q-8D |                           | <u> </u>                | _<br>_                        | <u> </u>                | <u> </u>                | _<br>_                    |

| -55°C to 125°C | 10 μV<br>20 μV      | TLC2654AM-8D<br>TLC2654M-8D | TLC2654AMJG<br>TLC2654MJG | TLC2654AMP<br>TLC2654MP | TLC2654AM-14D<br>TLC2654M-14D | TLC2654AMJ<br>TLC2654MJ | TLC2654AMN<br>TLC2654MN | TLC2654AMFK<br>TLC2654MFK |

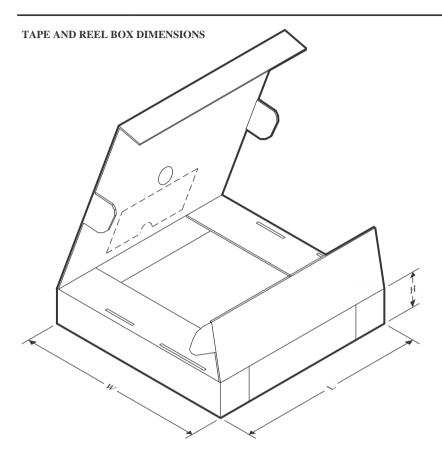

The 8-pin and 14-pin D packages are available taped and reeled. Add R suffix to device type (e.g., TLC2654AC-8DR).

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

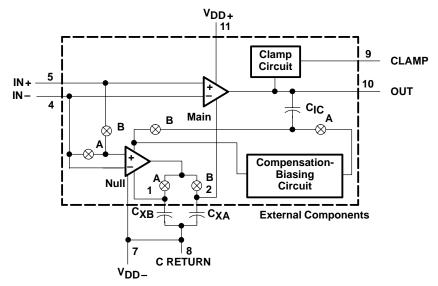

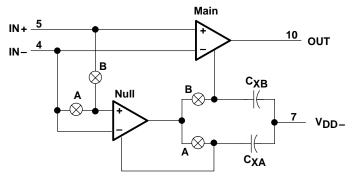

## functional block diagram

Pin numbers shown are for the D (14 pin), J, and N packages.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>DD+</sub> (see Note 1)                                                                        | 8 V                            |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Supply voltage, V <sub>DD</sub> (see Note 1)                                                                         | 8 V                            |

| Differential input voltage, V <sub>ID</sub> (see Note 2)                                                             |                                |

| Input voltage, V <sub>I</sub> (any input, see Note 1)                                                                | ±8 V                           |

| Voltage range on CLK IN and INT/EXT                                                                                  | $V_{DD-}$ to $V_{DD-} + 5.2 V$ |

| Input current, I <sub>I</sub> (each input)                                                                           |                                |

| Output current, IO                                                                                                   |                                |

| Duration of short-circuit current at (or below) 25°C (see Note 3)                                                    |                                |

| Current into CLK IN and INT/EXT                                                                                      |                                |

|                                                                                                                      |                                |

| Continuous total dissipation                                                                                         |                                |

| Continuous total dissipation                                                                                         |                                |

| Operating free-air temperature range, T <sub>A</sub> : C suffix                                                      |                                |

| Operating free-air temperature range, T <sub>A</sub> : C suffix                                                      | 0°C to 70°C                    |

| Operating free-air temperature range, T <sub>A</sub> : C suffix                                                      | 0°C to 70°C –40°C to 85°C      |

| Operating free-air temperature range, T <sub>A</sub> : C suffix                                                      |                                |

| Operating free-air temperature range, T <sub>A</sub> : C suffix                                                      |                                |

| Operating free-air temperature range, T <sub>A</sub> : C suffix I suffix Q suffix M suffix Storage temperature range |                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values, except differential voltages, are with respect to the midpoint between VDD+ and VDD-.

- 2. Differential voltages are at IN+ with respect to IN-.

- 3. The output may be shorted to either supply. Temperature and/or supply voltages must be limited to ensure that the maximum dissipation rating is not exceeded.

#### **DISSIPATION RATING TABLE**

| PACKAGE    | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|------------|----------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| D (8 pin)  | 725 mW                                             | 5.8 mW/°C                                      | 464 mW                                | 377 mW                                | 145 mW                                 |

| D (14 pin) | 950 mW                                             | 7.6 mW/°C                                      | 608 mW                                | 494 mW                                | 190 mW                                 |

| FK         | 1375 mW                                            | 11.0 mW/°C                                     | 880 mW                                | 715 mW                                | 275 mW                                 |

| J          | 1375 mW                                            | 11.0 mW/°C                                     | 880 mW                                | 715 mW                                | 275 mW                                 |

| JG         | 1050 mW                                            | 8.4 mW/°C                                      | 672 mW                                | 546 mW                                | 210 mW                                 |

| N          | 1150 mW                                            | 9.2 mW/°C                                      | 736 mW                                | 598 mW                                | 230 mW                                 |

| Р          | 1000 mW                                            | 8.0 mW/°C                                      | 640 mW                                | 520 mW                                | 200 mW                                 |

## recommended operating conditions

|                                            | С         | SUFFIX                | 18        | SUFFIX                | Q         | SUFFIX                | М         | SUFFIX                | UNIT |

|--------------------------------------------|-----------|-----------------------|-----------|-----------------------|-----------|-----------------------|-----------|-----------------------|------|

|                                            | MIN       | MAX                   | MIN       | MAX                   | MIN       | MAX                   | MIN       | MAX                   | UNIT |

| Supply voltage, V <sub>DD±</sub>           | ±2.3      | ±8                    | ±2.3      | ±8                    | ±2.3      | ±8                    | ±2.3      | ±8                    | V    |

| Common-mode input voltage, V <sub>IC</sub> | $V_{DD-}$ | V <sub>DD+</sub> -2.3 | V    |

| Clock input voltage                        | $V_{DD-}$ | V <sub>DD-</sub> +5   | $V_{DD-}$ | V <sub>DD</sub> _+5   | $V_{DD-}$ | V <sub>DD-</sub> +5   | $V_{DD-}$ | V <sub>DD-</sub> +5   | V    |

| Operating free-air temperature, TA         | 0         | 70                    | -40       | 85                    | -40       | 125                   | -55       | 125                   | °C   |

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

# electrical characteristics at specified free-air temperature, $V_{DD\pm}$ = $\pm 5$ V (unless otherwise noted)

|                  | DADAMETED                                            | TEOT 00                                     | NOTIONO                | - +              | Т               | LC26540 | 3    | TL              | .C2654A | С    |                    |

|------------------|------------------------------------------------------|---------------------------------------------|------------------------|------------------|-----------------|---------|------|-----------------|---------|------|--------------------|

|                  | PARAMETER                                            | I EST CO                                    | NDITIONS               | T <sub>A</sub> † | MIN             | TYP     | MAX  | MIN             | TYP     | MAX  | UNIT               |

| VIO              | Input offset voltage                                 |                                             |                        | 25°C             |                 | 5       | 20   |                 | 4       | 10   | μV                 |

| ۷IO              | (see Note 4)                                         |                                             |                        | Full range       |                 |         | 34   |                 |         | 24   | μν                 |

| αΛΙΟ             | Temperature coefficient of input offset voltage      |                                             |                        | Full range       |                 | 0.01    | 0.05 |                 | 0.01    | 0.05 | μV/°C              |

|                  | Input offset voltage<br>long-term drift (see Note 5) | V <sub>IC</sub> = 0,                        | $R_S = 50 \Omega$      | 25°C             |                 | 0.003   | 0.06 |                 | 0.003   | 0.02 | μV/mo              |

| li o             | Input offset current                                 | 1                                           |                        | 25°C             |                 | 30      | 60   |                 | 30      | 60   | - Δ                |

| ΙΟ               | input oilset current                                 |                                             |                        | Full range       |                 |         | 150  |                 |         | 150  | PΑ                 |

| lin              | Input bias current                                   |                                             |                        | 25°C             |                 | 50      | 60   |                 | 50      | 60   | nΔ                 |

| ΙΒ               | input bias current                                   |                                             |                        | Full range       |                 |         | 150  |                 |         | 150  | PΑ                 |

| V <sub>ICR</sub> | Common-mode input voltage range                      | $R_S = 50 \Omega$                           |                        | Full range       | -5<br>to<br>2.7 |         |      | -5<br>to<br>2.7 |         |      | V                  |

| .,               | Maximum positive peak                                | D 4010                                      | One Nata O             | 25°C             | 4.7             | 4.8     |      | 4.7             | 4.8     |      |                    |

| VOM+             | output voltage swing                                 | $R_L = 10 \text{ k}\Omega$ ,                | See Note 6             | Full range       | 4.7             |         |      | 4.7             |         |      | V                  |

| \/a              | Maximum negative peak                                | D 10 kO                                     | Coo Noto 6             | 25°C             | -4.7            | -4.9    |      | -4.7            | -4.9    |      | V                  |

| VOM-             | output voltage swing                                 | $R_L = 10 \text{ k}\Omega$ ,                | See Note 6             | Full range       | -4.7            |         |      | -4.7            |         |      | V                  |

| ۸. هـ            | Large-signal differential                            | \\o - +4\\                                  | R <sub>L</sub> = 10 kΩ | 25°C             | 120             | 155     |      | 135             | 155     |      | dВ                 |

| AVD              | voltage amplification                                | VO = ±4 V,                                  | IN_ = 10 K22           | Full range       | 120             |         |      | 130             |         |      | uБ                 |

|                  | Internal chopping frequency                          |                                             |                        | 25°C             |                 | 10      |      |                 | 10      |      | kHz                |

|                  | Clamp on-state current                               | R <sub>I</sub> = 100 kΩ                     |                        | 25°C             | 25              |         |      | 25              |         |      |                    |

|                  | Ciamp on-state current                               | K[ = 100 K22                                |                        | Full range       | 25              |         |      | 25              |         |      | μΑ                 |

|                  | Clamp off-state current                              | $V_{O} = -4 \text{ V to}$                   | 0.4.1/                 | 25°C             |                 |         | 100  |                 |         | 100  | nΛ                 |

|                  | Ciamp on-state current                               | VO = -4 V to                                | 0 4 V                  | Full range       |                 |         | 100  |                 |         | 100  | PΑ                 |

| CMRR             | Common-mode rejection                                | $V_0 = 0,$                                  | nin                    | 25°C             | 105             | 125     |      | 110             | 125     |      | ИD                 |

| CIVINA           | ratio                                                | $V_{IC} = V_{ICR}$ min,<br>RS = 50 $\Omega$ |                        | Full range       | 105             |         |      | 110             |         |      | uБ                 |

| kovo             | Supply voltage rejection                             | 1 1 DD = = = = 1.0 1 to = 0 1;              | 25°C                   | 110              | 125             |         | 110  | 125             |         | dВ   |                    |

| ksvr             | ratio (ΔV <sub>DD±</sub> /ΔV <sub>IO</sub> )         |                                             | Full range             | 110              |                 |         | 110  |                 |         | GD.  |                    |

| lDD              | Supply current                                       | Vo = 0                                      | No load                | 25°C             |                 | 1.5     | 2.4  |                 | 1.5     | 2.4  | μV/mo pA pA V V dB |

| -טט              | Cappi) carroin                                       | $V_O = 0,$                                  | . 10 1000              | Full range       |                 |         | 2.5  |                 |         | 2.5  |                    |

†Full range is 0°C to 70°C.

NOTES: 4. This parameter is not production tested full range. Thermocouple effects preclude measurement of the actual V<sub>IO</sub> of these devices in high-speed automated testing. V<sub>IO</sub> is measured to a limit determined by the test equipment capability at the temperature extremes. The test ensures that the stabilization circuitry is performing properly.

5. Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at T<sub>A</sub> = 150°C extrapolated to T<sub>A</sub> = 25° using the Arrhenius equation and assuming an activation energy of 0.96 eV.

6. Output clamp is not connected.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## operating characteristics at specified free-air temperature, $V_{DD\pm}$ = $\pm 5~V$

|        | PARAMETER                        | TEST                                                                     | T. †           | Τl  | C26540 | ;   | TL  | C2654A | С   | LINUT              |

|--------|----------------------------------|--------------------------------------------------------------------------|----------------|-----|--------|-----|-----|--------|-----|--------------------|

|        | PARAMETER                        | CONDITIONS                                                               | CONDITIONS TAT |     | TYP    | MAX | MIN | TYP    | MAX | UNIT               |

| SR+    | Desitive claw rate at unity gain |                                                                          | 25°C           | 1.5 | 2      |     | 1.5 | 2      |     | \//uo              |

| SK+    | Positive slew rate at unity gain | $V_0 = \pm 2.3 \text{ V},$                                               | Full range     | 1.3 |        |     | 1.3 |        |     | V/μs               |

| SR-    | Negative slew rate at unity gain | $R_L = 10 \text{ k}\Omega$ ,<br>$C_L = 100 \text{ pF}$                   | 25°C           | 2.3 | 3.7    |     | 2.3 | 3.7    |     | V/µs               |

| SK-    | Negative siew rate at unity gain |                                                                          | Full range     | 1.7 |        |     | 1.7 |        |     | ν/μδ               |

| V      | Equivalent input noise voltage   | f = 10 Hz                                                                | 25°C           |     | 47     |     |     | 47     | 75  | nV/√ <del>Hz</del> |

| Vn     | (see Note 7)                     | f = 1 kHz                                                                | 25 C           |     | 13     |     |     | 13     |     | NV/VHZ             |

| V      | Peak-to-peak equivalent input    | f = 0 to 1 Hz                                                            | 25°C           |     | 0.5    |     |     | 0.5    |     | /                  |

| VN(PP) | noise voltage                    | f = 0 to 10 Hz                                                           | 25 0           |     | 1.5    |     |     | 1.5    |     | μV                 |

| In     | Equivalent input noise current   | f = 10 kHz                                                               | 25°C           |     | 0.004  |     |     | 0.004  |     | pA/√ <del>Hz</del> |

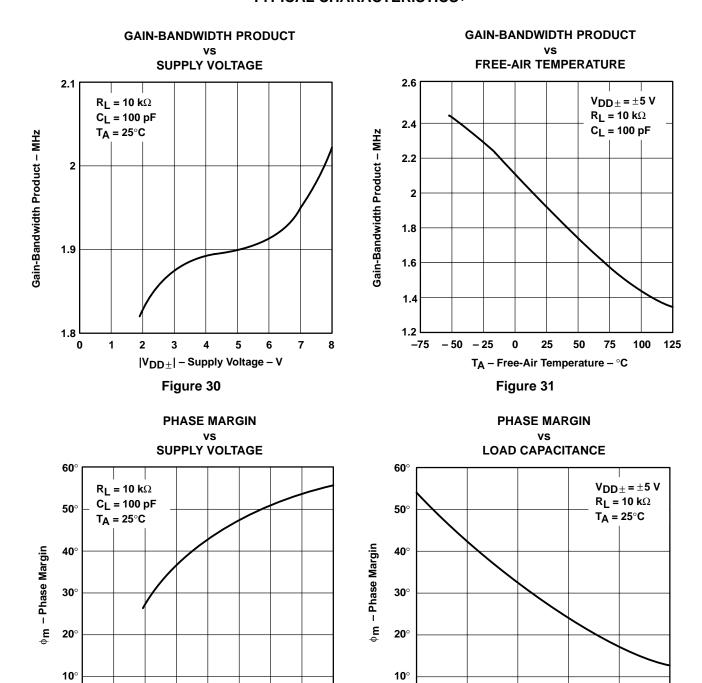

|        | Gain-bandwidth product           | $f = 10 \text{ kHz},$ $R_L = 10 \text{ k}\Omega,$ $C_L = 100 \text{ pF}$ | 25°C           |     | 1.9    |     |     | 1.9    |     | MHz                |

| φm     | Phase margin at unity gain       | $R_L = 10 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$                      | 25°C           |     | 48°    |     |     | 48°    |     |                    |

<sup>†</sup> Full range is 0°C to 70°C.

NOTE 7: This parameter is tested on a sample basis for the TLC2654A. For other test requirements, please contact the factory. This statement has no bearing on testing or nontesting of other parameters.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

# electrical characteristics at specified free-air temperature, V $_{DD\,\pm}$ = $\pm5$ V (unless otherwise noted)

|      | DADAMETED                                         | TECT COL                                     | UDITIONS              | - +              | Т               | LC2654 |      | T               | LC2654A | /I   | UNIT  |

|------|---------------------------------------------------|----------------------------------------------|-----------------------|------------------|-----------------|--------|------|-----------------|---------|------|-------|

|      | PARAMETER                                         | I ESI COI                                    | NDITIONS              | T <sub>A</sub> † | MIN             | TYP    | MAX  | MIN             | TYP     | MAX  | UNII  |

| VIO  | Input offset voltage                              |                                              |                       | 25°C             |                 | 5      | 20   |                 | 4       | 10   | μV    |

| VIO  | (see Note 4)                                      |                                              |                       | Full range       |                 |        | 40   |                 |         | 30   | μν    |

| αΝΙΟ | Temperature coefficient of input offset voltage   |                                              |                       | Full range       |                 | 0.01   | 0.05 |                 | 0.01    | 0.05 | μV/°C |

|      | Input offset voltage long-term drift (see Note 5) | V <sub>IC</sub> = 0,                         | R <sub>S</sub> = 50 Ω | 25°C             |                 | 0.003  | 0.06 |                 | 0.003   | 0.02 | μV/mo |

| lio. | Input offset current                              |                                              |                       | 25°C             |                 | 30     | 60   |                 | 30      | 60   | pА    |

| ΙΟ   | input onset current                               |                                              |                       | Full range       |                 |        | 200  |                 |         | 200  | pΑ    |

| Iв   | Input bias current                                |                                              |                       | 25°C             |                 | 50     | 60   |                 | 50      | 60   | pА    |

| אוי  | input bias current                                |                                              |                       | Full range       |                 |        | 200  |                 |         | 200  | PΛ    |

| VICR | Common-mode input voltage range                   | R <sub>S</sub> = 50 Ω                        |                       | Full range       | -5<br>to<br>2.7 |        |      | -5<br>to<br>2.7 |         |      | V     |

| 1/   | Maximum positive peak                             | D 4010                                       | O - Note O            | 25°C             | 4.7             | 4.8    |      | 4.7             | 4.8     |      |       |

| VOM+ | output voltage swing                              | $R_L = 10 \text{ k}\Omega$ , See Note        |                       | Full range       | 4.7             |        |      | 4.7             |         |      | V     |

| V    | Maximum negative peak                             | $R_{I} = 10 \text{ k}\Omega$ , See Note 6    |                       | 25°C             | -4.7            | -4.9   |      | -4.7            | -4.9    |      | V     |

| VOM- | output voltage swing                              |                                              | See Note 0            | Full range       | -4.7            |        |      | -4.7            |         |      | V     |

| AVD  | Large-signal differential                         | V <sub>O</sub> = ±4 V,                       | Pr = 10 kO            | 25°C             | 120             | 155    |      | 135             | 155     |      | dB    |

| ^VD  | voltage amplification                             | VO = ±4 V,                                   | IVE = 10 K22          | Full range       | 120             |        |      | 125             |         |      | uБ    |

|      | Internal chopping frequency                       |                                              |                       | 25°C             |                 | 10     |      |                 | 10      |      | kHz   |

|      | Clamp on-state current                            | R <sub>I</sub> = 100 kΩ                      |                       | 25°C             | 25              |        |      | 25              |         |      | μА    |

|      | Ciamp on-state current                            |                                              |                       | Full range       | 25              |        |      | 25              |         |      | μΑ    |

|      | Clamp off-state current                           | $V_0 = -4 \text{ V to}$                      | 5.4.V                 | 25°C             |                 |        | 100  |                 |         | 100  | pА    |

|      | Clamp on-state current                            | VO = -4 V W                                  | ) + V                 | Full range       |                 |        | 100  |                 |         | 100  | PΛ    |

| CMRR | Common-mode rejection                             | $V_0 = 0$ ,<br>$V_0 = V_{10}$                | nin                   | 25°C             | 105             | 125    |      | 110             | 125     |      | dB    |

|      | ratio                                             | $V_{IC} = V_{ICR}$ min,<br>$R_S = 50 \Omega$ |                       | Full range       | 105             |        |      | 110             |         |      |       |

| keyp | Supply voltage rejection                          | $V_{DD\pm} = \pm 2.3$                        |                       | 25°C             | 110             | 125    |      | 110             | 125     |      | dB    |

| ksvr | ratio (ΔV <sub>DD±</sub> /ΔV <sub>IO</sub> )      |                                              |                       | Full range       | 110             |        |      | 110             |         |      | ub    |

| lDD  | Supply current                                    | $V_{O} = 0$ ,                                | No load               | 25°C             |                 | 1.5    | 2.4  |                 | 1.5     | 2.4  | mA    |

| -טט  |                                                   | .0 = 0,                                      | . 10 1000             | Full range       |                 |        | 2.5  |                 |         | 2.5  |       |

†Full range is -40°C to 85°C

NOTES: 4. This parameter is not production tested full range. Thermocouple effects preclude measurement of the actual V<sub>IO</sub> of these devices in high-speed automated testing. V<sub>IO</sub> is measured to a limit determined by the test equipment capability at the temperature extremes. The test ensures that the stabilization circuitry is performing properly.

6. Output clamp is not connected.

<sup>5.</sup> Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at T<sub>A</sub> = 150°C extrapolated to T<sub>A</sub> = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## operating characteristics at specified free-air temperature, $V_{DD\pm}$ = $\pm 5~V$

|        | PARAMETER                        | TEST                                                                     | <b>T.</b> †      | T   | LC2654 |     | TL  | .C2654A | I   |                    |

|--------|----------------------------------|--------------------------------------------------------------------------|------------------|-----|--------|-----|-----|---------|-----|--------------------|

|        | PARAMETER                        | CONDITIONS                                                               | T <sub>A</sub> † | MIN | TYP    | MAX | MIN | TYP     | MAX | UNIT               |

| SR+    | Positive slew rate at unity gain |                                                                          | 25°C             | 1.5 | 2      |     | 1.5 | 2       |     | V/μs               |

| SINT   | Fositive siew rate at unity gain | $V_0 = \pm 2.3 \text{ V},$                                               | Full range       | 1.2 |        |     | 1.2 |         |     | ν/μ5               |

| SR-    | Negative slew rate at unity gain | $R_L = 10 \text{ k}\Omega$ ,<br>$C_L = 100 \text{ pF}$                   | 25°C             | 2.3 | 3.7    |     | 2.3 | 3.7     |     | V/μs               |

| SK-    | Negative siew rate at unity gain |                                                                          | Full range       | 1.5 |        |     | 1.5 |         |     | ν/μδ               |

| V      | Equivalent input noise voltage   | f = 10 Hz                                                                | 25°C             |     | 47     |     |     | 47      | 75  | ->///II-           |

| Vn     | (see Note 7)                     | f = 1 kHz                                                                | 25 C             |     | 13     |     |     | 13 20   |     | nV/√Hz             |

| V      | Peak-to-peak equivalent input    | f = 0 to 1 Hz                                                            | 25°C             |     | 0.5    |     |     | 0.5     |     | /                  |

| VN(PP) | noise voltage                    | f = 0 to 10 Hz                                                           | 25°C             |     | 1.5    |     |     | 1.5     |     | μV                 |

| In     | Equivalent input noise current   | f = 10 kHz                                                               | 25°C             |     | 0.004  |     |     | 0.004   |     | pA/√ <del>Hz</del> |

|        | Gain-bandwidth product           | $f = 10 \text{ kHz},$ $R_L = 10 \text{ k}\Omega,$ $C_L = 100 \text{ pF}$ | 25°C             |     | 1.9    |     |     | 1.9     |     | MHz                |

| φm     | Phase margin at unity gain       | $R_L = 10 \text{ k}\Omega$ ,<br>$C_L = 100 \text{ pF}$                   | 25°C             |     | 48°    |     |     | 48°     |     |                    |

<sup>†</sup>Full range is -40°C to 85°C.

NOTE 7: This parameter is tested on a sample basis for the TLC2654A. For other test requirements, please contact the factory. This statement has no bearing on testing or nontesting of other parameters.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

# electrical characteristics at specified free-air temperature, V<sub>DD $\pm$ </sub> = $\pm 5$ V (unless otherwise noted)

|                  | PARAMETER                                         | TEST CONDITIONS                                             | T <sub>A</sub> †    |                 | LC26540<br>LC26541 |       |                 | .C2654A<br>.C2654A |       | UNIT  |

|------------------|---------------------------------------------------|-------------------------------------------------------------|---------------------|-----------------|--------------------|-------|-----------------|--------------------|-------|-------|

|                  |                                                   |                                                             | '^                  | MIN             | TYP                | MAX   | MIN             | TYP                | MAX   |       |

| \/ı0             | Input offset voltage                              |                                                             | 25°C                |                 | 5                  | 20    |                 | 4                  | 10    | μV    |

| VIO              | (see Note 4)                                      |                                                             | Full range          |                 |                    | 50    |                 |                    | 40    | μν    |

| αVIO             | Temperature coefficient of input offset voltage   |                                                             | Full range          |                 | 0.01               | 0.05* |                 | 0.01               | 0.05* | μV/°C |

|                  | Input offset voltage long-term drift (see Note 5) | $V_{IC} = 0$ , $R_S = 50 \Omega$                            | 25°C                |                 | 0.003              | 0.06* |                 | 0.003              | 0.02* | μV/mo |

| lio              | Input offset current                              |                                                             | 25°C                |                 | 30                 | 60    |                 | 30                 | 60    | pА    |

| '10              | input onset current                               | ]                                                           | Full range          |                 |                    | 500   |                 |                    | 500   | PΑ    |

| I <sub>IB</sub>  | Input bias current                                |                                                             | 25°C                |                 | 50                 | 60    |                 | 50                 | 60    | pА    |

| סוי              | input bias carrent                                |                                                             | Full range          |                 |                    | 500   |                 |                    | 500   | P/ \  |

| VICR             | Common-mode input voltage range                   | R <sub>S</sub> = 50 Ω                                       | Full range          | -5<br>to<br>2.7 |                    |       | -5<br>to<br>2.7 |                    |       | V     |

| .,               | Maximum positive peak                             | D 4010 0 N 4 0                                              | 25°C                | 4.7             | 4.8                |       | 4.7             | 4.8                |       | .,    |

| V <sub>OM+</sub> | output voltage swing                              | $R_L = 10 \text{ k}\Omega$ , See Note 6                     | Full range          | 4.7             |                    |       | 4.7             |                    |       | V     |

| .,               | Maximum negative peak                             | D 40 lo Can Nata C                                          | 25°C -4.7 -4.9 -4.7 |                 | -4.7               | -4.9  |                 | V                  |       |       |

| VOM-             | output voltage swing                              | $R_L = 10 \text{ k}\Omega$ , See Note 6                     | Full range          | -4.7            |                    |       | -4.7            |                    |       | V     |

| AVD              | Large-signal differential                         | $V_{\Omega} = \pm 4 \text{ V},  R_{I} = 10 \text{ k}\Omega$ | 25°C                | 120             | 155                |       | 135             | 155                |       | dB    |

| ^VD              | voltage amplification                             | VO = ±4 V, KL = 10 K22                                      | Full range          | 120             |                    |       | 120             |                    |       | uБ    |

|                  | Internal chopping frequency                       |                                                             | 25°C                |                 | 10                 |       |                 | 10                 |       | kHz   |

|                  | Clamp on-state current                            | R <sub>L</sub> = 100 kΩ                                     | 25°C                | 25              |                    |       | 25              |                    |       | μА    |

|                  | Clamp on-state current                            | IVE = 100 K22                                               | Full range          | 25              |                    |       | 25              |                    |       | μΛ    |

|                  | Clamp off-state current                           | $V_0 = -4 \text{ V to } 4 \text{ V}$                        | 25°C                |                 |                    | 100   |                 |                    | 100   | pА    |

|                  | Olding on state durient                           | VO = 4 V 10 4 V                                             | Full range          |                 |                    | 500   |                 |                    | 500   | P/ \  |

| CMRR             | Common-mode rejection                             | $V_O = 0$ ,                                                 | 25°C                | 105             | 125                |       | 110             | 125                |       | dB    |

| CIVIKK           | ratio                                             | $V_{IC} = V_{ICR}$ min,<br>$R_S = 50 \Omega$ Fu             |                     | 105             |                    |       | 110             |                    |       | uв    |

| ksvr             | Supply voltage rejection                          | $V_{DD\pm} = \pm 2.3 \text{ V to } \pm 8 \text{ V},$        | 25°C                | 110             | 125                |       | 110             | 125                |       | dB    |

| ··ovk            | ratio ( $\Delta V_{DD\pm}/\Delta V_{IO}$ )        | $V_O = 0$ , $R_S = 50 \Omega$                               | Full range          | 105             |                    |       | 110             |                    |       | 45    |

| lDD              | Supply current                                    | $V_O = 0$ , No load                                         | 25°C                |                 | 1.5                | 2.4   |                 | 1.5                | 2.4   | mΑ    |

| יטט              |                                                   | - U 0, 110.0dd                                              | Full range          |                 |                    | 2.5   |                 |                    | 2.5   |       |

<sup>\*</sup> On products complaint to MIL-STD-883, Class B, this parameter is not production tested.

6. Output clamp is not connected.

<sup>†</sup> Full range is -40° to 125°C for Q suffix, -55° to 125°C for M suffix.

NOTES: 4. This parameter is not production tested full range. Thermocouple effects preclude measurement of the actual V<sub>IO</sub> of these devices in high-speed automated testing. V<sub>IO</sub> is measured to a limit determined by the test equipment capability at the temperature extremes. The test ensures that the stabilization circuitry is performing properly.

<sup>5.</sup> Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at T<sub>A</sub> = 150°C extrapolated to T<sub>A</sub> = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## operating characteristics at specified free-air temperature, $V_{DD\pm}$ = $\pm 5~V$

|                                        | PARAMETER                         | TEST CONDITIONS                                                             | T <sub>A</sub> † | TL: | C2654Q<br>C2654M<br>C2654A<br>C2654A | Q                                           | UNIT                 |

|----------------------------------------|-----------------------------------|-----------------------------------------------------------------------------|------------------|-----|--------------------------------------|---------------------------------------------|----------------------|

|                                        |                                   |                                                                             |                  | MIN | TYP                                  | MAX                                         |                      |

| SR+                                    | Desitive along rate at unity sain |                                                                             | 25°C             | 1.5 | 2                                    |                                             | 1////                |

| SK+                                    | Positive slew rate at unity gain  | Va 122V B. 40k0 C. 400 F                                                    | Full range       | 1.1 |                                      |                                             | V/μs                 |

| CD. No matical aless and a trunits and |                                   | $V_O = \pm 2.3 \text{ V},  R_L = 10 \text{ k}\Omega,  C_L = 100 \text{ pF}$ | 25°C             | 2.3 | 3.7                                  |                                             | 1////                |

| SR-                                    | Negative slew rate at unity gain  |                                                                             | Full range       | 1.3 |                                      | 3.7<br>47<br>13<br>0.5<br>1.5<br>004<br>1.9 | V/μs                 |

| ,,                                     | Equivalent input paige valtage    | f = 10 Hz                                                                   | 25°C             |     | 47                                   |                                             | ->44/ <del>11=</del> |

| V <sub>n</sub>                         | Equivalent input noise voltage    | f = 1 kHz                                                                   | 25°C             |     | 13                                   |                                             | nV/√Hz               |

| V                                      | Peak-to-peak equivalent input     | f = 0 to 1 Hz                                                               | 25°C             |     | 0.5                                  |                                             | \/                   |

| V <sub>N(PP)</sub>                     | noise voltage                     | f = 0 to 10 Hz                                                              | 25°C             |     | 1.5                                  |                                             | μV                   |

| In                                     | Equivalent input noise current    | f = 1 kHz                                                                   | 25°C             |     | 0.004                                |                                             | pA/√ <del>Hz</del>   |

|                                        | Gain-bandwidth product            | $f = 10 \text{ kHz}, 	 R_L = 10 \text{ k}\Omega, 	 C_L = 100 \text{ pF}$    | 25°C             |     | 1.9                                  |                                             | MHz                  |

| φm                                     | Phase margin at unity gain        | $R_L = 10 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$                         | 25°C             |     | 48°                                  |                                             |                      |

<sup>†</sup> Full range is -40° to 125°C for Q suffix, -55° to 125°C for M suffix.

## **TYPICAL CHARACTERISTICS**

## **Table of Graphs**

|                    |                                                 |                                                                                  | FIGURE      |

|--------------------|-------------------------------------------------|----------------------------------------------------------------------------------|-------------|

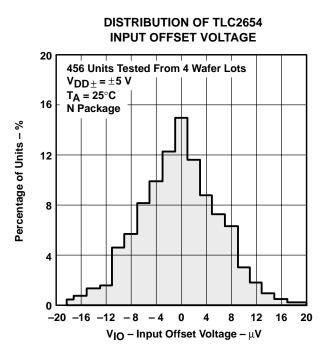

| V <sub>IO</sub>    | Input offset voltage                            | Distribution                                                                     | 2           |

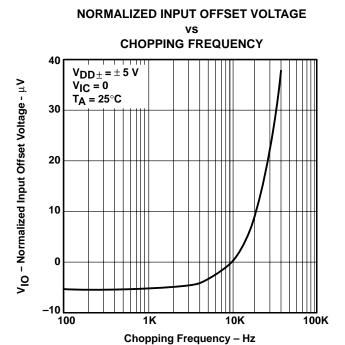

|                    | Normalized input offset voltage                 | vs Chopping frequency                                                            | 3           |

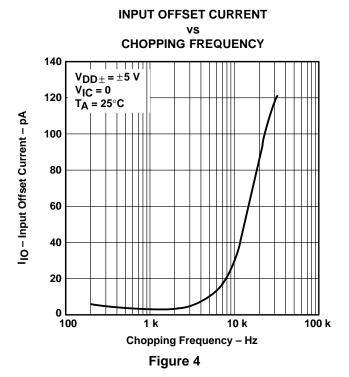

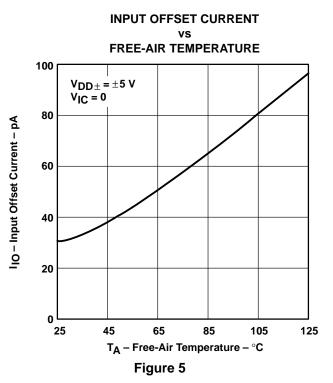

| ΙΙΟ                | Input offset current                            | vs Chopping frequency vs Free-air temperature                                    | 4<br>5      |

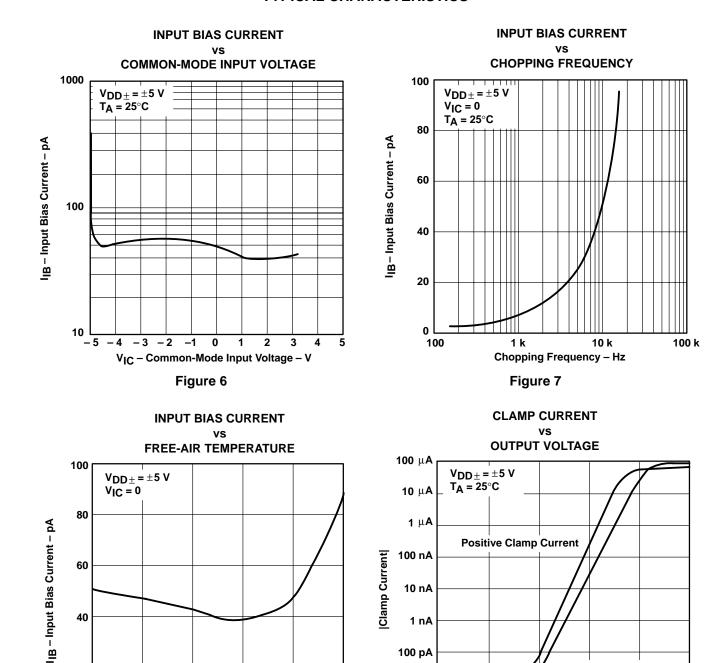

| I <sub>IB</sub>    | Input bias current                              | vs Common-mode input voltage<br>vs Chopping frequency<br>vs Free-air temperature | 6<br>7<br>8 |

|                    | Clamp current                                   | vs Output voltage                                                                | 9           |

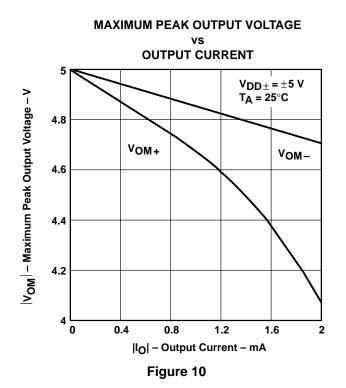

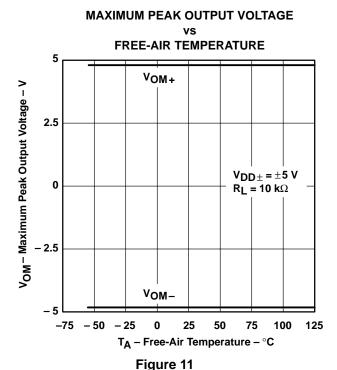

| V <sub>OM</sub>    | Maximum peak output voltage swing               | vs Output current<br>vs Free-air temperature                                     | 10<br>11    |

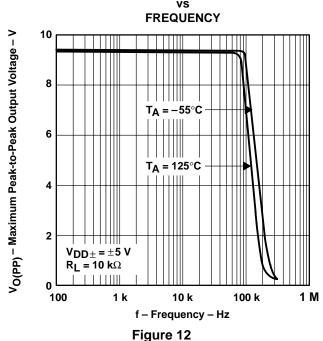

| VO(PP)             | Maximum peak-to-peak output voltage swing       | vs Frequency                                                                     | 12          |

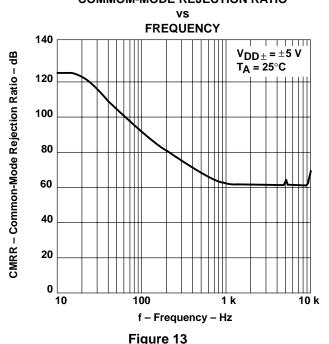

| CMRR               | Common-mode rejection ratio                     | vs Frequency                                                                     | 13          |

| AVD                | Large-signal differential voltage amplification | vs Frequency<br>vs Free-air temperature                                          | 14<br>15    |

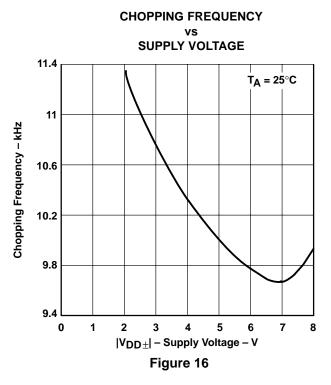

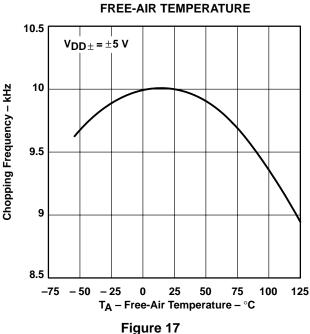

|                    | Chopping frequency                              | vs Supply voltage<br>vs Free-air temperature                                     | 16<br>17    |

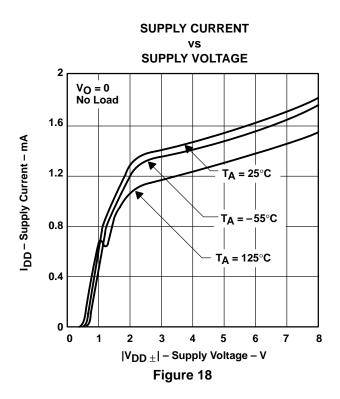

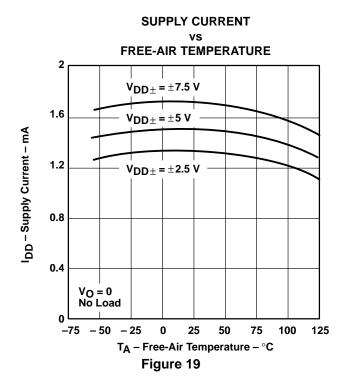

| IDD                | Supply current                                  | vs Supply voltage<br>vs Free-air temperature                                     | 18<br>19    |

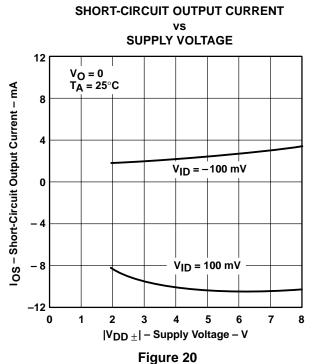

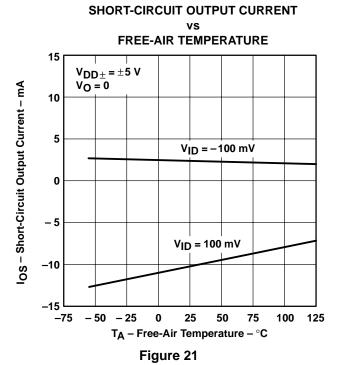

| los                | Short-circuit output current                    | vs Supply voltage<br>vs Free-air temperature                                     | 20<br>21    |

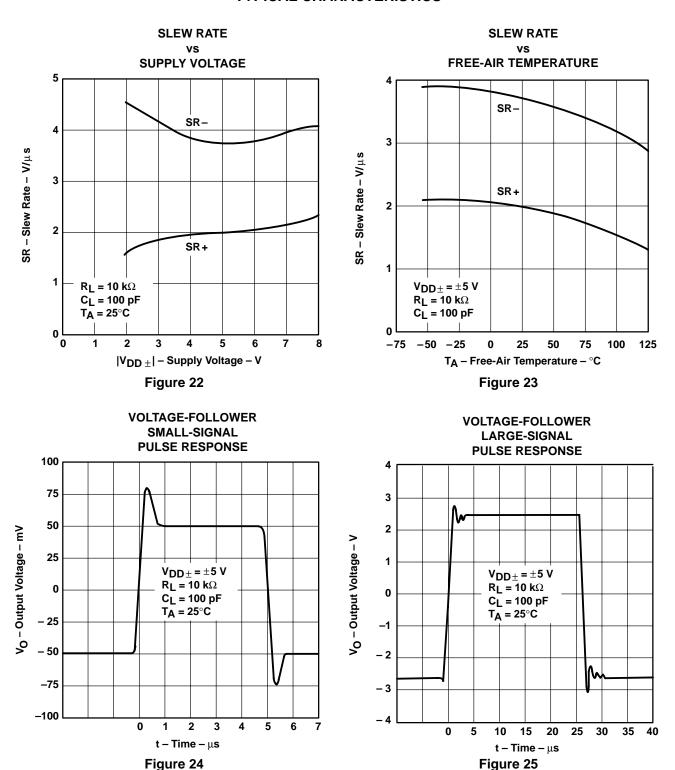

| SR                 | Slew rate                                       | vs Supply voltage<br>vs Free-air temperature                                     | 22<br>23    |

|                    | Voltage-follower pulse response                 | Small signal<br>Large signal                                                     | 24<br>25    |

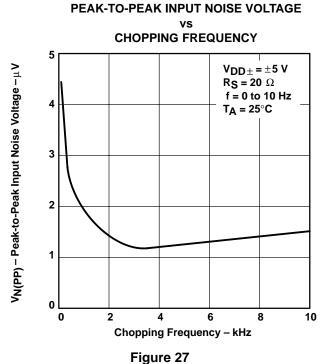

| V <sub>N(PP)</sub> | Peak-to-peak input noise voltage                | vs Chopping frequency                                                            | 26, 27      |

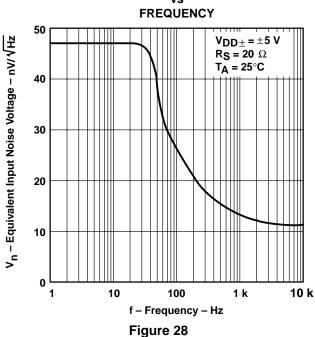

| ٧n                 | Equivalent input noise voltage                  | vs Frequency                                                                     | 28          |

| ksvr               | Supply voltage rejection ratio                  | vs Frequency                                                                     | 29          |

|                    | Gain-bandwidth product                          | vs Supply voltage<br>vs Free-air temperature                                     | 30<br>31    |

| φm                 | Phase margin                                    | vs Supply voltage<br>vs Load capacitance                                         | 32<br>33    |

|                    | Phase shift                                     | vs Frequency                                                                     | 14          |

Figure 2

Figure 3

<sup>†</sup>Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

125

105

20

0

25

45

T<sub>A</sub> - Free-Air Temperature - °C Figure 8

100 pA

10 pA

1 pA

4

4.2

4.4

Figure 9

|VO| - Output Voltage - V

5

**Negative Clamp Current**

4.8

4.6

<sup>†</sup>Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

# **MAXIMUM PEAK-TO-PEAK OUTPUT VOLTAGE**

## **COMMOM-MODE REJECTION RATIO**

†Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

#### LARGE-SIGNAL DIFFERENTIAL VOLTAGE **AMPLIFICATION AND PHASE SHIFT** vs **FREQUENCY** A<sub>VD</sub>' – Large-Signal Differential Voltage Amplification – dB 60° 120 100 **Phase Shift** 80° 80 100° $A_{VD}$ 60 120° Phase Shift 40 140° 20 160° $V_{DD\pm} = \pm 5 V$ 180° $R_L = 10 \text{ k}\Omega$ $C_{I} = 100 pF$ -20 200° T<sub>A</sub> = 25°C 220° 100 10 k 100 k 10 M 10 1 k f - Frequency - Hz Figure 14

LARGE-SIGNAL DIFFERENTIAL **VOLTAGE AMPLIFICATION** vs FREE-AIR TEMPERATURE A<sub>VD</sub> - Large-Signal Differential Voltage Amplification - dB 160  $V_{DD\pm} = \pm 5 V$  $R_L = 10 \text{ k}\Omega$ V<sub>O</sub> = ±4 V 158 156 154 152 150 75 - 50 - 25 25 50 100 75 125

# **CHOPPING FREQUENCY**

$T_A$  – Free-Air Temperature –  ${}^{\circ}C$

Figure 15

†Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## TYPICAL CHARACTERISTICS<sup>†</sup>

†Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

<sup>†</sup>Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

#### TYPICAL CHARACTERISTICS

## PEAK-TO-PEAK INPUT NOISE VOLTAGE **CHOPPING FREQUENCY** 1.8 $V_{N(PP)}$ – Peak-to-Peak Input Noise Voltage – $\mu V$ $V_{DD\pm} = \pm 5 V$ $R_S = 20 \Omega$ 1.6 f = 0 to 1 Hz $T_A = 25^{\circ}C$ 1.4 1.2 1 8.0 0.6 0.4 0.2 0 0 2 6 8 10 Chopping Frequency - kHz

## **EQUIVALENT INPUT NOISE VOLTAGE** vs **FREQUENCY**

Figure 26

Figure 29

f - Frequency - Hz

1 k

10 k

20

0

10

7

**0**°

0

3

4

$|V_{DD\pm}|$  – Supply Voltage – V

Figure 32

5

0° ∟ 0

200

400

Figure 33

600

C<sub>L</sub> - Load Capacitance - pF

800

1000

<sup>†</sup>Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## **APPLICATION INFORMATION**

## capacitor selection and placement

Leakage and dielectric absorption are the two important factors to consider when selecting external capacitors  $C_{XA}$  and  $C_{XB}$ . Both factors can cause system degradation, negating the performance advantages realized by using the TLC2654.

Degradation from capacitor leakage becomes more apparent with increasing temperatures. Low-leakage capacitors and standoffs are recommended for operation at  $T_A = 125$ °C. In addition, guard bands are recommended around the capacitor connections on both sides of the printed-circuit board to alleviate problems caused by surface leakage on circuit boards.

Capacitors with high dielectric absorption tend to take several seconds to settle upon application of power, which directly affects input offset voltage. In applications needing fast settling of input voltage, high-quality film capacitors such as mylar, polystyrene, or polypropylene should be used. In other applications, a ceramic or other low-grade capacitor can suffice.

Unlike many choppers available today, the TLC2654 is designed to function with values of  $C_{XA}$  and  $C_{XB}$  in the range of 0.1  $\mu$ F to 1  $\mu$ F without degradation to input offset voltage or input noise voltage. These capacitors should be located as close as possible to  $C_{XA}$  and  $C_{XB}$  and return to either  $V_{DD-}$  or C RETURN. On many choppers, connecting these capacitors to  $V_{DD-}$  causes degradation in noise performance; this problem is eliminated on the TLC2654.

#### internal/external clock

The TLC2654 has an internal clock that sets the chopping frequency to a nominal value of 10 kHz. On 8-pin packages, the chopping frequency can only be controlled by the internal clock; however, on all 14-pin packages and the 20-pin FK package the device chopping frequency can be set by the internal clock or controlled externally by use of the INT/EXT and CLK IN. To use the internal 10-kHz clock, no connection is necessary. If external clocking is desired, connect INT/EXT to V<sub>DD</sub> and the external clock to CLK IN. The external clock trip point is 2.5 V above the negative rail; however, CLK IN can be driven from the negative rail to 5 V above the negative rail. This allows the TLC2654 to be driven directly by 5-V TTL and CMOS logic when operating in the single-supply configuration. If this 5-V level is exceeded, damage could occur to the device unless the current

into CLK IN is limited to  $\pm 5$  mA. A divide-by-two frequency divider interfaces with CLK IN and sets the chopping frequency. The chopping frequency appears on CLK OUT.

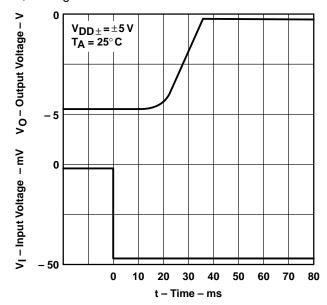

## overload recovery/output clamp

When large differential-input-voltage conditions are applied to the TLC2654, the nulling loop attempts to prevent the output from saturating by driving  $C_{XA}$  and  $C_{XB}$  to internally-clamped voltage levels. Once the overdrive condition is removed, a period of time is required to allow the built-up charge to dissipate. This time period is defined as overload recovery time (see Figure 34). Typical overload recovery time for the TLC2654 is significantly faster than competitive products; however, this time can be reduced further by use of internal clamp circuitry accessible through CLAMP if required.

Figure 34. Overload Recovery

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

#### **APPLICATION INFORMATION**

## overload recovery/output clamp (continued)

The clamp is a switch that is automatically activated when the output is approximately 1 V from either supply rail. When connected to the inverting input (in parallel with the closed-loop feedback resistor), the closed-loop gain is reduced and the TLC2654 output is prevented from going into saturation. Since the output must source or sink current through the switch (see Figure 9), the maximum output voltage swing is slightly reduced.

#### thermoelectric effects

To take advantage of the extremely low offset voltage temperature coefficient of the TLC2654, care must be taken to compensate for the thermoelectric effects present when two dissimilar metals are brought into contact with each other (such as device leads being soldered to a printed-circuit board). It is not uncommon for dissimilar metal junctions to produce thermoelectric voltages in the range of several microvolts per degree Celsius (orders of magnitude greater than the  $0.01~\mu\text{V}/^\circ\text{C}$  typical of the TLC2654).

To help minimize thermoelectric effects, pay careful attention to component selection and circuit-board layout. Avoid the use of nonsoldered connections (such as sockets, relays, switches, etc.) in the input signal path. Cancel thermoelectric effects by duplicating the number of components and junctions in each device input. The use of low-thermoelectric-coefficient components, such as wire-wound resistors, is also beneficial.

## latch-up avoidance

Because CMOS devices are susceptible to latch-up due to their inherent parasitic thyristors, the TLC2654 inputs and outputs are designed to withstand -100-mA surge currents without sustaining latch-up; however, techniques to reduce the chance of latch-up should be used whenever possible. Internal protection diodes should not, by design, be forward biased. Applied input and output voltages should not exceed the supply voltage by more than 300 mV. Care should be exercised when using capacitive coupling on pulse generators. Supply transients should be stunted by the use of decoupling capacitors (0.1  $\mu$ F typical) located across the supply rails as close to the device as possible.

The current path established if latch-up occurs is usually between the supply rails and is limited only by the impedance of the power supply and the forward resistance of the parasitic thyristor. The chance of latch-up occurring increases with increasing temperature and supply voltage.

#### electrostatic-discharge protection

The TLC2654 incorporates internal ESD-protection circuits that prevent functional failures at voltages at or below 2000 V. Care should be exercised in handling these devices, as exposure to ESD may result in degradation of the device parametric performance.

## theory of operation

Chopper-stabilized operational amplifiers offer the best dc performance of any monolithic operational amplifier. This superior performance is the result of using two operational amplifiers — a main amplifier and a nulling amplifier – plus oscillator-controlled logic and two external capacitors to create a system that behaves as a single amplifier. With this approach, the TLC2654 achieves submicrovolt input offset voltage, submicrovolt noise voltage, and offset voltage variations with temperature in the nV/°C range.

The TLC2654 on-chip control logic produces two dominant clock phases: a nulling phase and an amplifying phase. The term chopper-stabilized derives from the process of switching between these two clock phases. Figure 35 shows a simplified block diagram of the TLC2654. Switches A and B are make-before-break types.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

## **APPLICATION INFORMATION**

## theory of operation (continued)

During the nulling phase, switch A is closed, shorting the nulling amplifier inputs together and allowing the nulling amplifier to reduce its own input offset voltage by feeding its output signal back to an inverting input node. Simultaneously, external capacitor  $C_{XA}$  stores the nulling potential to allow the offset voltage of the amplifier to remain nulled during the amplifying phase.

Pin numbers shown are for the D (14 pin), J, and N packages.

Figure 35. TLC2654 Simplified Block Diagram

During the amplifying phase, switch B is closed, connecting the output of the nulling amplifier to a noninverting input of the main amplifier. In this configuration, the input offset voltage of the main amplifier is nulled. Also, external capacitor  $C_{XB}$  stores the nulling potential to allow the offset voltage of the main amplifier to remain nulled during the next nulling phase.

This continuous chopping process allows offset voltage nulling during variations in time and temperature and over the common-mode input voltage range and power supply range. In addition, because the low-frequency signal path is through both the null and main amplifiers, extremely high gain is achieved.

The low-frequency noise of a chopper amplifier depends on the magnitude of the component noise prior to chopping and the capability of the circuit to reduce this noise while chopping. The use of the Advanced LinCMOS process, with its low-noise analog MOS transistors and patent-pending input stage design, significantly reduces the input noise voltage.

The primary source of nonideal operation in chopper-stabilized amplifiers is error charge from the switches. As charge imbalance accumulates on critical nodes, input offset voltage can increase especially with increasing chopping frequency. This problem has been significantly reduced in the TLC2654 by use of a patent-pending compensation circuit and the Advanced LinCMOS process.

The TLC2654 incorporates a feed-forward design that ensures continuous frequency response. Essentially, the gain magnitude of the nulling amplifier and compensation network crosses unity at the break frequency of the main amplifier. As a result, the high-frequency response of the system is the same as the frequency response of the main amplifier. This approach also ensures that the slewing characteristics remain the same during both the nulling and amplifying phases.

The primary limitation on ac performance is the chopping frequency. As the input signal frequency approaches the chopper's clock frequency, intermodulation (or aliasing) errors result from the mixing of these frequencies. To avoid these error signals, the input frequency must be less than half the clock frequency. Most choppers available today limit the internal chopping frequency to less than 500 Hz in order to eliminate errors due to the charge imbalancing phenomenon mentioned previously. However, to avoid intermodulation errors on a 500-Hz chopper, the input signal frequency must be limited to less than 250 Hz.

SLOS020G - NOVEMBER 1988 - REVISED APRIL 2001

#### **APPLICATION INFORMATION**

## theory of operation (continued)

The TLC2654 removes this restriction on ac performance by using a 10-kHz internal clock frequency. This high chopping frequency allows amplification of input signals up to 5 kHz without errors due to intermodulation and greatly reduces low-frequency noise.

#### THERMAL INFORMATION

## temperature coefficient of input offset voltage

Figure 36 shows the effects of package-included thermal EMF. The TLC2654 can null only the offset voltage within its nulling loop. There are metal-to-metal junctions outside the nulling loop (bonding wires, solder joints, etc.) that produce EMF. In Figure 36, a TLC2654 packaged in a 14-pin plastic package (N package) was placed in an oven at 25°C at t = 0, biased up, and allowed to stabilize. At t = 3 min, the oven was turned on and allowed to rise in temperature to 125°C. As evidenced by the curve, the overall change in input offset voltage with temperature is less than the specified maximum limit of  $0.05~\mu\text{V}/^{\circ}\text{C}$ .

Figure 36. Effects of Package-Induced Thermal EMF

www.ti.com 2-Dec-2023

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| 5962-9089504QPA  | ACTIVE     | CDIP         | JG                 | 8    | 50             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 9089504QPA<br>TLC2654AM | Samples |

| TLC2654AC-8D     | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | 2654AC                  | Samples |

| TLC2654ACP       | ACTIVE     | PDIP         | Р                  | 8    | 50             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type | 0 to 70      | TLC2654AC               | Samples |

| TLC2654AI-8D     | LIFEBUY    | SOIC         | D                  | 8    | 75             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | 2654AI                  |         |

| TLC2654AIP       | LIFEBUY    | PDIP         | Р                  | 8    | 50             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type |              | TLC2654AI               |         |

| TLC2654AMJGB     | ACTIVE     | CDIP         | JG                 | 8    | 50             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 9089504QPA<br>TLC2654AM | Samples |

| TLC2654C-14DR    | LIFEBUY    | SOIC         | D                  | 14   | 2500           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | TLC2654C                |         |

| TLC2654C-8D      | LIFEBUY    | SOIC         | D                  | 8    | 75             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | 2654C                   |         |

| TLC2654C-8DR     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | 2654C                   | Samples |

| TLC2654CN        | LIFEBUY    | PDIP         | N                  | 14   | 25             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type | 0 to 70      | TLC2654CN               |         |

| TLC2654CP        | LIFEBUY    | PDIP         | Р                  | 8    | 50             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type |              | TLC2654CP               |         |

| TLC2654I-8D      | LIFEBUY    | SOIC         | D                  | 8    | 75             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | 26541                   |         |

| TLC2654I-8DR     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 26541                   | Samples |

| TLC2654IP        | LIFEBUY    | PDIP         | Р                  | 8    | 50             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type |              | TLC2654IP               |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

PACKAGE OPTION ADDENDUM

www.ti.com 2-Dec-2023

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TLC2654A, TLC2654AM:

Catalog: TLC2654A

Military: TLC2654AM

NOTE: Qualified Version Definitions:

Catalog - TI's standard catalog product

• Military - QML certified for Military and Defense Applications

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

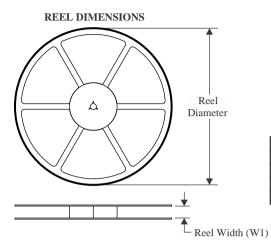

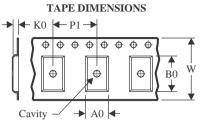

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

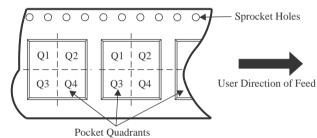

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLC2654C-14DR | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| TLC2654C-8DR  | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TLC2654I-8DR  | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

## \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLC2654C-14DR | SOIC         | D               | 14   | 2500 | 350.0       | 350.0      | 43.0        |

| TLC2654C-8DR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TLC2654I-8DR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

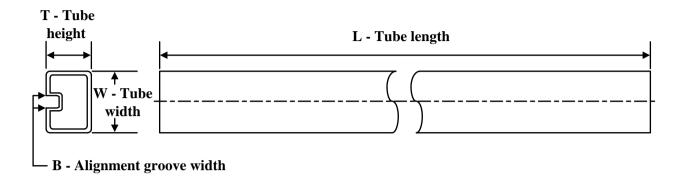

## **TUBE**

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TLC2654AC-8D | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLC2654AC-8D | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TLC2654ACP   | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| TLC2654AI-8D | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TLC2654AI-8D | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLC2654AIP   | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| TLC2654C-8D  | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TLC2654C-8D  | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLC2654CN    | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TLC2654CP    | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| TLC2654I-8D  | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TLC2654I-8D  | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLC2654IP    | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

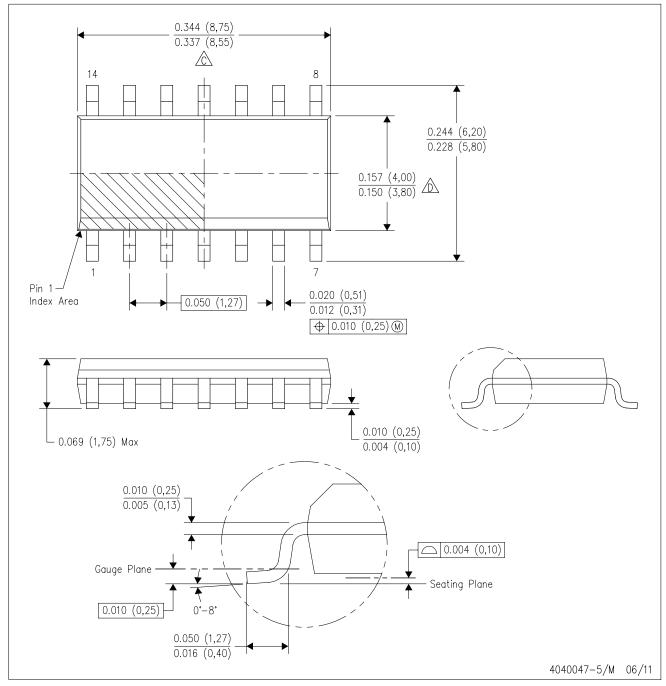

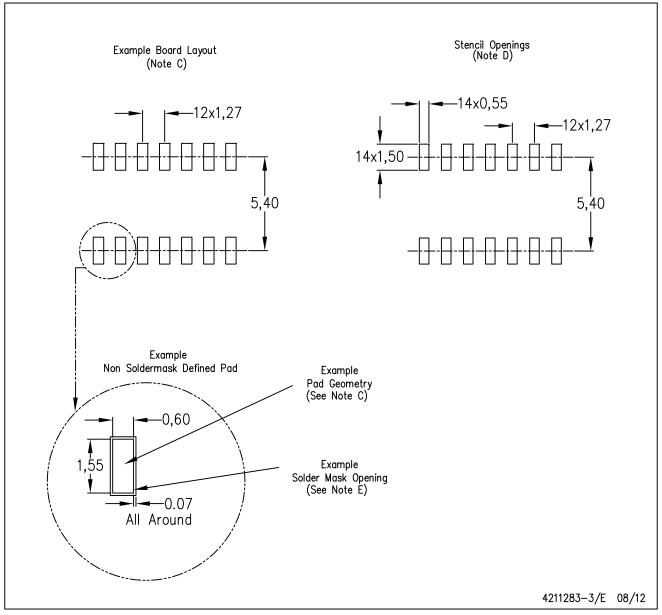

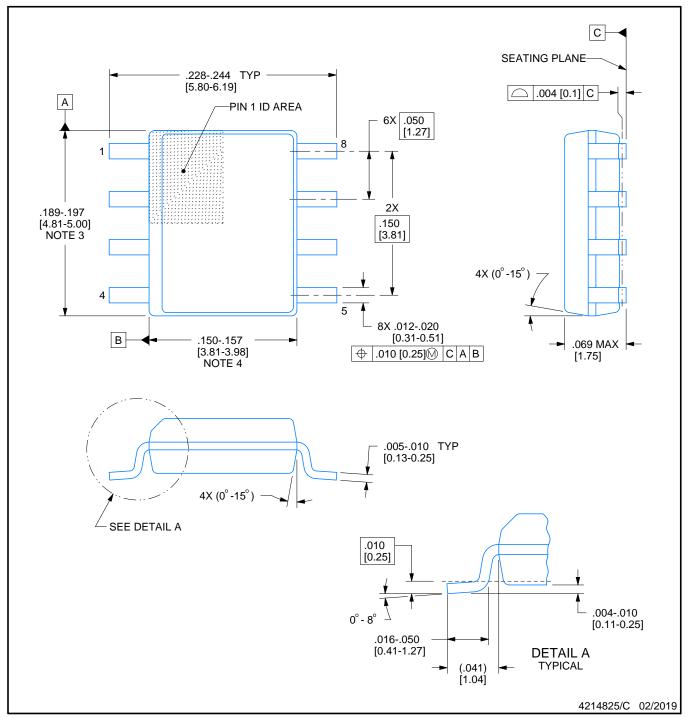

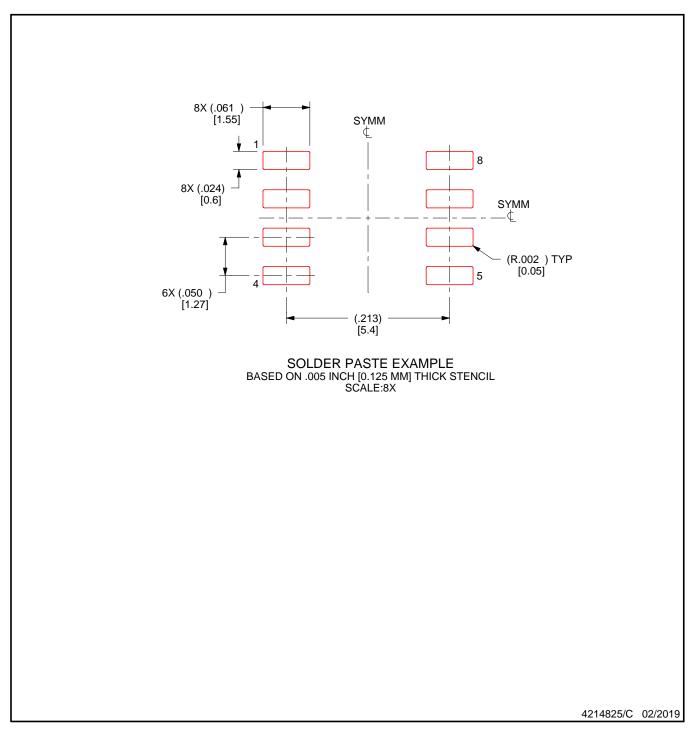

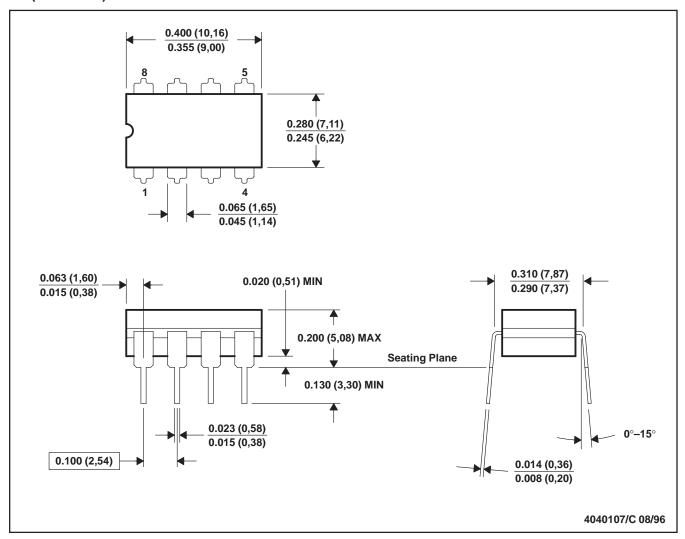

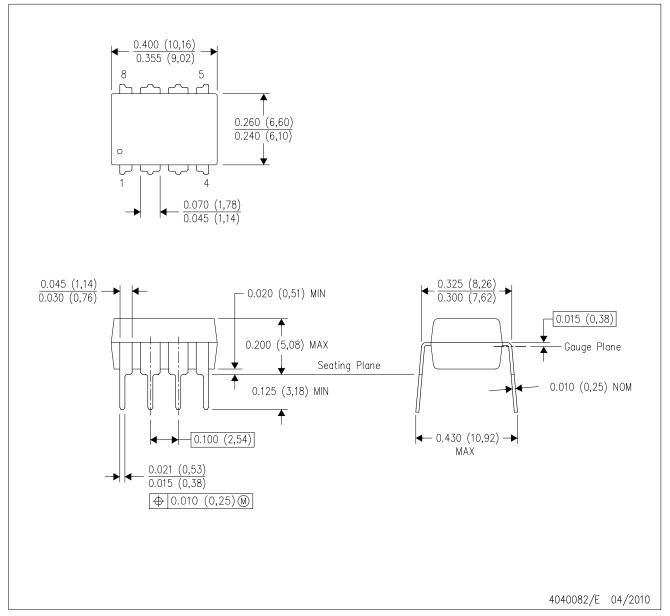

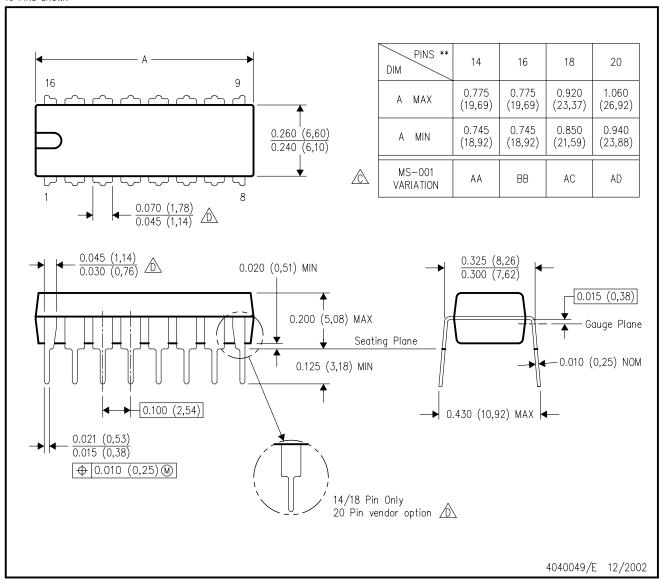

# D (R-PDSO-G14)

## PLASTIC SMALL OUTLINE