#### SN74ALVC16601 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS

JANUARY 1993

- Member of the Texas Instruments

Widebus™ Family

- UBT™ (Universal Bus Transceiver)

Combines D-Type Latches and D-Type

Flip-Flops for Operation in Transparent,

Latched, Clocked, or Clock-Enabled Mode

- EPIC™ (Enhanced-Performance Implanted CMOS) Submicron Process

- Designed to Facilitate Incident Wave Switching for Line Impedances of 50  $\Omega$  or Greater

- Typical V<sub>OLP</sub> (Output Ground Bounce)

< 0.8 V at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C

- Typical V<sub>OHV</sub> (Output V<sub>OH</sub> Undershoot)

2 V at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C

- ESD Protection Exceeds 2000 V Per MIL-STD-883C, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

- Latch-Up Performance Exceeds 250 mA Per JEDEC Standard JESD-17

- Package Options Include Plastic 300-mil Shrink Small-Outline and Thin Shrink Small-Outline Packages

#### description

This 18-bit universal bus transceiver is designed for 2.7-V to 3.6-V  $V_{CC}$  operation.

The SN74ALVC16601 combines D-type latches and D-type flip-flops to allow data flow in transparent, latched, and clocked modes.

### DGG OR DL PACKAGE (TOP VIEW)

|                   |                |    | I                 |

|-------------------|----------------|----|-------------------|

| OEAB [            | ] <sub>1</sub> | 56 | CLKENAB           |

| LEAB [            | 2              |    | CLKAB             |

| A1 [              |                |    | B1                |

| GND [             | 4              | 53 | GND               |

| A2 [              | 5              | 52 | ] B2              |

| АЗ [              | 6              | 51 | ] B3              |

| v <sub>cc</sub> [ |                | 50 | $]v_{cc}$         |

| A4 [              |                |    | ] B4              |

| A5 [              |                |    | ] B5              |

| A6 [              |                |    | ] B6              |

| GND [             | 11             | 46 | ] GND             |

| A7 [              |                |    | <b>]</b> B7       |

|                   | 13             | 44 | ] B8              |

| A9 [              | 14             |    | ] B9              |

| A10 [             |                |    | ] B10             |

| A11 [             |                |    | ] B11             |

| A12 [             | 17             | 40 | ] B12             |

| GND [             |                | 39 | GND               |

| A13 [             | 19             | 38 | ] B13             |

| A14 [             | 20             |    | ] B14             |

| A15 [             |                |    | ] B15             |

| v <sub>cc</sub> [ | 22             | 35 | ] v <sub>cc</sub> |

| A16 [             |                | 34 | ] B16             |

| A17 [             | 24             | 33 | B17               |

| GND [             |                | 32 | [] GND            |

| A18 [             | 26             | 31 | B18               |

| OEBA [            |                | 30 | ] CLKBA           |

| LEBA [            | 28             | 29 | CLKENBA           |

|                   |                |    |                   |

Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs. The clock can be controlled by the clock-enable (CLKENAB and CLKENBA) inputs. For A-to-B data flow, the device operates in the transparent mode when LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is low, the A-bus data is stored in the latch/flip-flop on the high-to-low transition of CLKAB. Output enable OEAB is active low. When OEAB is low, the outputs are active. When OEAB is high, the outputs are in the high-impedance state.

Data flow for B to A is similar to that of A to B but uses OEBA, LEBA, CLKBA, and CLKENBA.

The SN74ALVC16601 is packaged in TI's shrink small-outline package (DL), which provides twice the I/O pin count and functionality of standard small-outline packages in the same printed-circuit-board area.

The SN74ALVC16601 is characterized for operation from -40°C to 85°C.

EPIC, UBT, and Widebus are trademarks of Texas Instruments Incorporated.

# SN74ALVC16601 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS JANUARY 1993

#### **FUNCTION TABLE<sup>†</sup>**

| INPUTS  |      |      |          |   | OUTPUT                               |

|---------|------|------|----------|---|--------------------------------------|

| CLKENAB | OEAB | LEAB | CLKAB    | Α | В                                    |

| Х       | Н    | Х    | Х        | Х | Z                                    |

| X       | L    | н    | Х        | L | L                                    |

| Х       | L    | н    | Х        | Н | н                                    |

| Н       | L    | L    | Х        | Х | B <sub>0</sub> ‡                     |

| Н       | L    | Ĺ    | Х        | X | В <sub>0</sub> ‡<br>В <sub>0</sub> ‡ |

| L       | L    | L    | <b>↑</b> | L | L                                    |

| L       | L    | L    | <b>↑</b> | Н | н                                    |

| L       | L    | L    | L        | X | B <sub>0</sub> ‡                     |

| L       | L    | L    | Н        | Χ | B <sub>0</sub> ‡<br>B <sub>0</sub> § |

<sup>†</sup> A-to-B data flow is shown: B-to-A flow is similar but uses OEBA, LEBA, CLKBA, and CLKENBA.

<sup>&</sup>lt;sup>‡</sup> Output level before the indicated steady-state input conditions were established.

<sup>§</sup> Output level before the indicated steady-state input conditions were established, provided that CLKAB was low before LEAB went low.

JANUARY 1993

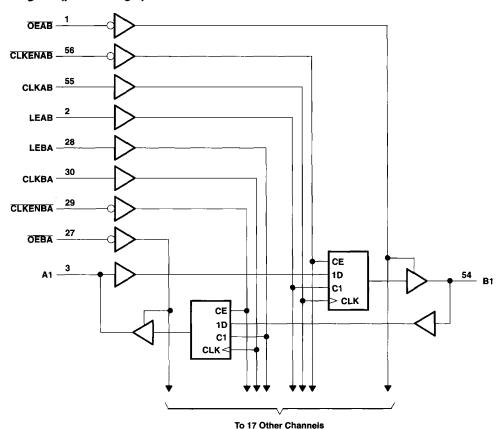

#### logic diagram (positive logic)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                                              | 0.5 V to 4.6 V                   |

|------------------------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> (except I/O ports) (see Note 1)                | 0.5 V to 4.6 V                   |

| Input voltage range, V <sub>I</sub> (I/O ports) (see Notes 1 and 2)                | . $-0.5$ V to $V_{CC}$ + $0.5$ V |

| Output voltage range, V <sub>O</sub> (see Notes 1 and 2)                           | . $-0.5$ V to $V_{CC}$ + $0.5$ V |

| Input clamp current, $I_{ K }(V_1 < 0)$                                            | –50 mA                           |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ )                     | ±50 mA                           |

| Continuous output current, I <sub>O</sub> (V <sub>O</sub> = 0 to V <sub>CC</sub> ) | ±50 mA                           |

| Continuous current through V <sub>CC</sub> or GND pins                             | ±100 mA                          |

| Maximum power dissipation at T <sub>A</sub> = 55°C (in still air): DGG package     | 0.7 W                            |

| DL package                                                                         |                                  |

| Storage temperature range                                                          | 65°C to 150°C                    |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2.</sup> This value is limited to 4.6 V maximum.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

#### SN74ALVC16601 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS

JANUARY 1993

#### recommended operating conditions (see Note 3)

|                 |                                                                     |     |      | UNIT |

|-----------------|---------------------------------------------------------------------|-----|------|------|

| V <sub>CC</sub> | Supply voltage                                                      | 2.7 | 3.6  | ٧    |

| V <sub>IH</sub> | High-level input voltage $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$ | 2   |      | ٧    |

| V <sub>IL</sub> | Low-level input voltage $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$  |     | 0.8  | ٧    |

| Vi              | Input voltage                                                       |     |      | ٧    |

| ٧o              | Output voltage                                                      |     |      | ٧    |

| Юн              | High-level output current                                           |     | -12  | mA   |

|                 | V <sub>CC</sub> = 3 V                                               |     | -24† | 100  |

| loL             | Low-level output current V <sub>CC</sub> = 2.7 V                    |     | 12   | mA   |

|                 | V <sub>CC</sub> = 3 V                                               |     | 24†  | "''  |

| Δt/Δν           | Input transition rise or fall rate                                  |     |      | ns/V |

| TA              | Operating free-air temperature                                      | -40 | 85   | °C   |

NOTE 3: Unused or floating pins (input or I/O) must be held high or low.

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PA               | RAMETER        | TEST CO                                                                   | NDITIONS                              | V <sub>CC</sub> ‡    | MIN | TYP | MAX              | UNIT |  |

|------------------|----------------|---------------------------------------------------------------------------|---------------------------------------|----------------------|-----|-----|------------------|------|--|

| V <sub>IK</sub>  |                | I <sub>I</sub> = -18 mA                                                   |                                       | 2.7 V                |     |     | -1.2             | ٧    |  |

| V <sub>OH</sub>  |                | $I_{OH} = -100 \mu\text{A}$ MIN to MAX $V_{CC}$                           |                                       | V <sub>CC</sub> -0.2 |     |     |                  |      |  |

|                  |                | I <sub>OH</sub> = –12 mA                                                  |                                       | 2.7 V                | 2.2 |     |                  | V    |  |

|                  |                |                                                                           |                                       | 3 V                  | 2.4 |     |                  |      |  |

|                  |                | I <sub>OH</sub> = −24 mA                                                  | 3 V                                   | 2                    |     |     |                  |      |  |

|                  |                | I <sub>QL</sub> = 100 μA                                                  |                                       | MIN to MAX           |     |     | 0.2              |      |  |

| V <sub>OL</sub>  |                | I <sub>OL</sub> = 12 mA                                                   |                                       | 2.7 V                |     |     | 0.4              | ٧    |  |

|                  |                | I <sub>OL</sub> = 24 mA                                                   |                                       | 3 V                  |     |     | 0.55             |      |  |

| 1                |                | V <sub>I</sub> = V <sub>CC</sub> or GND                                   |                                       | 3.6 V                |     |     | ±5               | μA   |  |

| loz§             |                | V <sub>O</sub> = V <sub>CC</sub> or GND                                   |                                       | 3.6 V                |     |     | ±10              | μΑ   |  |

| Icc              |                | V <sub>I</sub> = V <sub>CC</sub> or GND,                                  | I <sub>O</sub> = 0                    | 3.6 V                |     |     | 20               | μА   |  |

| Δl <sub>CC</sub> |                | $V_{CC} = 3 \text{ V to } 3.6 \text{ V},$ Other inputs at $V_{CC}$ or GND | One input at V <sub>CC</sub> – 0.6 V, |                      |     |     | 500              | μА   |  |

| Ci               | Control inputs | V <sub>I</sub> = V <sub>CC</sub> or GND                                   |                                       | 3.3 V                |     | TBD | , and the second | pF   |  |

| Cio              | A or B ports   | V <sub>O</sub> = V <sub>CC</sub> or GND                                   |                                       | 3.3 V                |     | TBD |                  | pF   |  |

<sup>&</sup>lt;sup>‡</sup> For conditions shown as MIN or MAX, use the appropriate values under recommended operating conditions.

<sup>&</sup>lt;sup>†</sup> Current duty cycle ≤ 50%, f ≥ 1 kHz

$<sup>\</sup>S$  For I/O ports, the parameter  $I_{\mbox{\scriptsize OZ}}$  includes the input leakage current.