# **Signetics**

## 74LS259 Latch

8-Bit Addressable Latch Product Specification

#### **Logic Products**

#### **FEATURES**

- Combines demultiplexer and 8-bit latch

- Serial-to-parallel capability

- Output from each storage bit available

- Random (addressable) data entry

- Easily expandable

- Common Clear input

- Useful as a 1-of-8 active HIGH decoder

#### DESCRIPTION

The '259 addressable latch has four distinct modes of operation that are selectable by controlling the Clear and Enable inputs (see Function Table). In the addressable latch mode, data at the Data (D) inputs is written into the addressed latches. The addressed latches will follow the Data input with all unaddressed latches remaining in their previous states. In the memory mode, all latches remain in their previous states and are unaffected by the Data or Address inputs. To eliminate the possibility of entering erroneous data in the

| TYPE    | TYPICAL PROPAGATION DELAY | TYPICAL SUPPLY CURRENT (TOTAL) |

|---------|---------------------------|--------------------------------|

| 74LS259 | 19ns                      | 22mA                           |

#### ORDERING CODE

| PACKAGES      | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V ±5%; T <sub>A</sub> = 0°C to +70°C |

|---------------|-----------------------------------------------------------------------------|

| Plastic DIP   | N74LS259N                                                                   |

| Plastic SO-16 | N74LS259D                                                                   |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74 <b>L</b> S |

|------|-------------|---------------|

| All  | Inputs      | 1LSul         |

| All  | Outputs     | 10LSul        |

#### NOT

A 74LS unit load (LSul) is 20 µA IIH and -0.4mA IIL.

latches, the enable should be held HIGH (inactive) while the address lines are changing. In the 1-of-8 decoding or demultiplexing mode ( $\overline{\text{CLR}} = \overline{\text{E}} = \text{LOW}$ ), addressed outputs will follow the level of

the D inputs, with all other outputs LOW. In the clear mode, all outputs are LOW and unaffected by the Address and Data inputs.

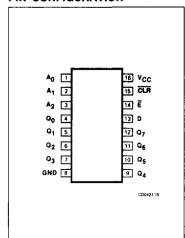

#### PIN CONFIGURATION

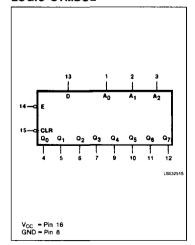

#### LOGIC SYMBOL

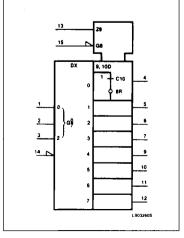

#### LOGIC SYMBOL (IEEE/IEC)

## Latch

74LS259

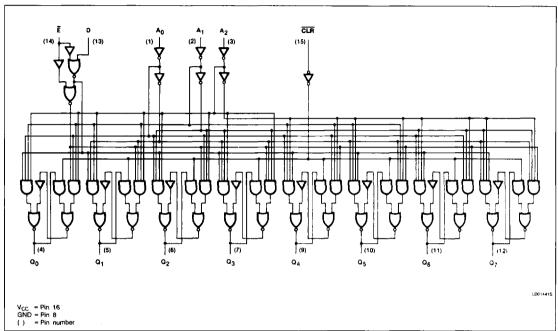

#### LOGIC DIAGRAM

#### MODE SELECT-FUNCTION TABLE

| OPERATING            |     | INPUTS |   |    |                | OUTPUTS        |                |                |                |                |                |                |                |                       |

|----------------------|-----|--------|---|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|

| MODE                 | CLR | Ē      | D | Ao | A <sub>1</sub> | A <sub>2</sub> | Qo             | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>4</sub> | Q <sub>5</sub> | Q <sub>6</sub> | Q <sub>7</sub>        |

| Clear                | L   | Н      | х | Х  | Х              | Х              | L              | L              | L              | L              | L              | L              | L              | L                     |

| ~                    | L   | L      | d | L  | L              | L              | Q = d          | L              | L              | L              | L              | L              | L              | L                     |

|                      | L   | Ĺ      | d | Н  | L              | L              | L              | Q = d          | L              | L              | L              | L              | L              | L                     |

| Demultiplex          | L   | L      | d | L  | H              | L              | L              | L              | Q = d          | L              | L              | L              | L              | L                     |

| (active HIGH decoder |     | •      | • | •  | •              |                | •              | •              | •              | •              | •              |                | •              |                       |

| when $D = H$ )       | •   | •      | • |    | •              |                | •              | ٠ ا            | •              | •              | •              |                |                | •                     |

|                      | •   | •      | • | •  | •              |                | •              |                | •              | •              | •              |                | •              | •                     |

|                      | L   | L      | d | Н  | н              | H              | L              | L              | L              | L              | L_             | L              | L              | Q = d                 |

| Store (do nothing)   | Н   | Н      | Х | Х  | Х              | х              | q <sub>0</sub> | q <sub>1</sub> | q <sub>2</sub> | q <sub>3</sub> | <b>Q</b> 4     | q <sub>5</sub> | <b>q</b> 6     | <b>q</b> <sub>7</sub> |

|                      | Н   | L      | d | L  | L              | L              | Q = d          | q <sub>1</sub> | q <sub>2</sub> | q <sub>3</sub> | 94             | <b>q</b> 5     | q <sub>6</sub> | 97                    |

|                      | н   | L      | d | Н  | L              | L              | qo             | Q = d          | q <sub>2</sub> | q <sub>3</sub> | 94             | q <sub>5</sub> | q <sub>6</sub> | <b>q</b> <sub>7</sub> |

|                      | н   | L      | ď | L  | н              | L              | 90             | q <sub>1</sub> | Q ≈ d          | q <sub>3</sub> | <b>Q</b> 4     | <b>q</b> 5     | q <sub>6</sub> | <b>q</b> <sub>7</sub> |

| Addressable latch    |     | •      |   |    | •              |                | •              |                |                | •              | •              |                |                |                       |

|                      | •   | •      |   | •  | •              |                | •              |                | •              | •              | •              |                | •              | •                     |

|                      | •   | •      |   | •  | •              |                | •              | ٠ ا            | •              | •              | •              |                |                | •                     |

|                      | Н , | L      | d | H  | Н              | H              | q <sub>0</sub> | q <sub>1</sub> | q <sub>2</sub> | q <sub>3</sub> | q <sub>4</sub> | <b>q</b> 5     | q <sub>6</sub> | Q = d                 |

H = HIGH voltage level steady state.

L = LOW voltage level steady state.

X = Don't care.

d = HIGH or LOW data one set-up time prior to the LOW-to-HIGH Enable transition.

q = Lower case letters indicate the state of the referenced output established during the last cycle in which it was addressed or cleared.

Latch 74LS259

#### ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted.)

|                 | PARAMETER                                      | 74LS                     | UNIT |

|-----------------|------------------------------------------------|--------------------------|------|

| V <sub>CC</sub> | Supply voltage                                 | 7.0                      | v    |

| V <sub>IN</sub> | Input voltage                                  | -0.5 to +7.0             | ٧    |

| I <sub>IN</sub> | Input current                                  | -30 to +1                | mA   |

| Vout            | Voltage applied to output in HIGH output state | -0.5 to +V <sub>CC</sub> | V    |

| TA              | Operating free-air temperature range           | 0 to 70                  | °C   |

#### RECOMMENDED OPERATING CONDITIONS

|                 | DARAMETER                      |      |     |       |      |

|-----------------|--------------------------------|------|-----|-------|------|

|                 | PARAMETER                      | Min  | Nom | Max   | UNIT |

| V <sub>CC</sub> | Supply voltage                 | 4.75 | 5.0 | 5.25  | ٧    |

| VIH             | HIGH-level input voltage       | 2.0  |     |       | ٧    |

| V <sub>IL</sub> | LOW-level input voltage        |      |     | + 0.8 | ٧    |

| l <sub>IH</sub> | Input clamp current            |      |     | -18   | mA.  |

| Гон             | HIGH-level output current      |      |     | -400  | μА   |

| loL             | LOW-level output current       |      |     | 8     | mA   |

| TA              | Operating free-air temperature | 0    |     | 70    | °C   |

## DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

|                 |                                           |                                                                                            | TEST COMPLETIONS             |     |      | 74LS259 |      |  |  |

|-----------------|-------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------|-----|------|---------|------|--|--|

| PARAMETER       |                                           | TEST CONL                                                                                  | TEST CONDITIONS1             |     |      | Max     | UNIT |  |  |

| V <sub>OH</sub> | HIGH-level output voltage                 | V <sub>CC</sub> = MIN, V <sub>IH</sub> = MIN, V <sub>IL</sub> = MAX, I <sub>OH</sub> = MAX |                              | 2.7 | 3.4  |         | ٧    |  |  |

| .,              | I ( )W-level output voltage               | V <sub>CC</sub> = MIN, V <sub>IH</sub> = MIN,                                              | I <sub>OL</sub> = MAX        |     | 0.35 | 0.5     | ٧    |  |  |

| V <sub>OL</sub> | LOW-level output voltage                  | V <sub>IL</sub> = MAX                                                                      | I <sub>OL</sub> = 4mA (74LS) |     | 0.25 | 0.4     | ٧    |  |  |

| VIK             | Input clamp voltage                       | $V_{CC} = MIN, I_1 = I_{IK}$                                                               |                              |     |      | -1.5    | ٧    |  |  |

| l <sub>i</sub>  | Input current at maximum input voltage    | V <sub>CC</sub> = MAX, V <sub>I</sub> = 7.0V                                               |                              |     |      | 0.1     | mA   |  |  |

| l <sub>IH</sub> | HIGH-level input current                  | $V_{CC} = MAX, V_1 = 2.7V$                                                                 |                              |     |      | 20      | μΑ   |  |  |

| l <sub>IL</sub> | LOW-level input current                   | $V_{CC} = MAX, V_1 = 0.4V$                                                                 |                              |     |      | ~0.4    | mA   |  |  |

| los             | Short-circuit output current <sup>3</sup> | V <sub>CC</sub> = MAX                                                                      |                              | -20 |      | -100    | mA   |  |  |

| Icc             | Supply current <sup>4</sup> (total)       | V <sub>CC</sub> = MAX                                                                      |                              |     | 22   | 36      | mA   |  |  |

#### NOTES:

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

<sup>2.</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$  °C.

<sup>3.</sup> Ios is tested with V<sub>OUT</sub> = +0.5V and V<sub>CC</sub> = V<sub>CC</sub> MAX + 0.5V. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

<sup>4.</sup> Measure I<sub>CC</sub> with the inputs grounded and the outputs open.

Latch 74LS259

### AC ELECTRICAL CHARACTERISTICS TA = 25°C, VCC = 5.0V

| PARAMETER                            |                                        |                 | 74                    | UNIT     |    |

|--------------------------------------|----------------------------------------|-----------------|-----------------------|----------|----|

|                                      |                                        | TEST CONDITIONS | C <sub>L</sub> = 15pF |          |    |

|                                      |                                        |                 | Min                   | Max      |    |

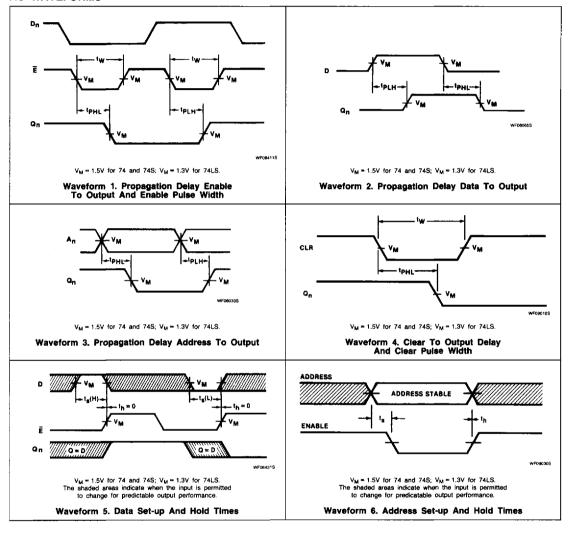

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Enable to output  | Waveform 1      |                       | 35<br>24 | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay Data to output       | Waveform 2      |                       | 32<br>21 | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Address to output | Waveform 3      |                       | 38<br>29 | ns |

| t <sub>PHL</sub>                     | Propagation delay, clear to output     | Waveform 4      |                       | 27       | ns |

#### AC SET-UP REQUIREMENTS

|                    |                                               | TEST COMPLETIONS |     | 74LS |      |  |

|--------------------|-----------------------------------------------|------------------|-----|------|------|--|

|                    | PARAMETER                                     | TEST CONDITIONS  | Min | Max  | UNIT |  |

| tw                 | Enable pulse width                            | Waveform 1       | 15  |      | ns   |  |

| tw                 | Clear pulse width                             | Waveform 4       | 15  |      | ns   |  |

| t <sub>s</sub> (H) | Set-up time HIGH, data to enable              | Waveform 5       | 15  |      | ns   |  |

| t <sub>h</sub> (H) | Hold time HIGH, data to enable                | Waveform 5       | 5   |      | ns   |  |

| t <sub>s</sub> (L) | Set-up time LOW, data to enable               | Waveform 5       | 15  |      | ns   |  |

| t <sub>h</sub> (L) | Hold time LOW, data to enable                 | Waveform 5       | 5   |      | ns   |  |

| t <sub>s</sub>     | Set-up time, address to enable <sup>(a)</sup> | Waveform 6       | 15  |      | ns   |  |

| th                 | Hold time, address to enable(b)               | Waveform 6       | 15  |      | ns   |  |

#### NOTES:

a. The Address to Enable set-up time is the time before the HiGH-to-LOW Enable transition that the Address must be stable so that the correct latch is addressed and the other latches are not affected.

b. The Address to Enable hold time is the time after the LOW-to-HIGH Enable transition that the Address must be stable so that the correct latch is addressed and the other latches are not affected.

Latch 74LS259

#### **AC WAVEFORMS**

#### E

## Latch

74LS259

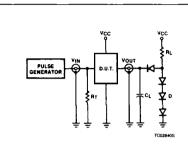

#### TEST CIRCUITS AND WAVEFORMS

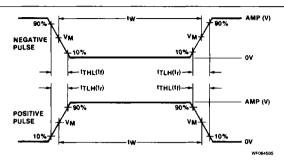

$V_M = 1.3V$  for 74LS;  $V_M = 1.5V$  for all other TTL families.

#### Test Circuit For 74 Totem-Pole Outputs

#### Input Pulse Definition

#### DEFINITIONS

$R_L$  = Load resistor to  $V_{CC}$ ; see AC CHARACTERISTICS for value.  $C_L$  = Load capacitance includes jig and probe capacitance;

- see AC CHARACTERISTICS for value.

R<sub>T</sub> = Termination resistance should be equal to Z<sub>OUT</sub> of Pulse Generators.

- D = Diodes are 1N916, 1N3064, or equivalent.

- $t_{\text{TLH.}}\ t_{\text{THL}}$  Values should be less than or equal to the table entries.

| F4480 V | INPUT PULSE REQUIREMENTS |           |             |                  |                  |  |  |  |

|---------|--------------------------|-----------|-------------|------------------|------------------|--|--|--|

| FAMILY  | Amplitude                | Rep. Rate | Pulse Width | t <sub>TLH</sub> | t <sub>THL</sub> |  |  |  |

| 74      | 3.0V                     | 1MHz      | 500ns       | 7ns              | 7ns              |  |  |  |

| 74LS    | 3.0V                     | 1MHz      | 500ns       | 15ns             | 6ns              |  |  |  |

| 74S     | 3.0V                     | 1MHz      | 500ns       | 2.5ns            | 2.5ns            |  |  |  |