June 2014

# 74LVX3245 8-Bit, Dual-Supply Translating Transceiver with 3-State Outputs

#### **Features**

- Bidirectional Interface Between 3 V and 5 V Buses

- Inputs Compatible with TTL Level

- 3 V Data Flow at A-Port and 5 V Data Flow at B-Port

- Outputs Source / Sink: 24 mA

- Guaranteed Simultaneous Switching Noise Level and Dynamic Threshold Performance

- Implements Proprietary EMI Reduction Circuitry

- Functionally Compatible with the 74 Series 245

## **Description**

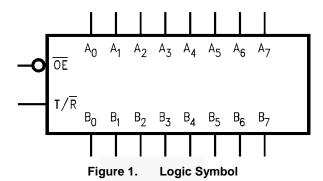

The 74LVX3245 is a dual-supply, 8-bit translating transceiver designed to interface between a 3 V bus and a 5 V bus in a mixed 5 V supply environment. The Transmit/ Receive (T/R) input determines the direction of data flow. Transmit (active-HIGH) enables data from A-ports to B-ports; receive (active-LOW) enables data from B-ports to A-ports. The output enable input, when HIGH, disables both A- and B-ports by placing them in a high-impedance condition. The A-port interfaces with the 3 V bus; the B-port interfaces with the 5 V bus.

The 74LVX3245 is suitable for mixed-voltage applications, such as notebook computers using 3.3 V CPU and 5V peripheral components.

## **Related Resources**

AN-5001 — Using Fairchild's LVX Low-Voltage Dual-Supply CMOS Translating Transceivers

## **Ordering Information**

| Part Number   | Operating<br>Temperature Range | Package                                       | Packing Method |

|---------------|--------------------------------|-----------------------------------------------|----------------|

| 74LVX3245WM   |                                | 24-Lead Small-Outline Integrated Circuit      | Tubes          |

| 74LVX3245WMX  | 2                              | (SOIC), JEDEC MS-013, 0.300" Wide             | Tape and Reel  |

| 74LVX3245QSC  |                                | 24-Lead Quarter-Size Outline Package          | Tubes          |

| 74LVX3245QSCX | -40 to +85°C                   | (QSOP), JEDEC MO-137, 0.150" Wide             | Tape and Reel  |

| 74LVX3245MTC  |                                | 24-Lead Thin-Shrink Small-Outline             | Tubes          |

| 74LVX3245MTCX |                                | Package (TSSOP), JEDEC MO-153,<br>4.4 mm Wide | Tape and Reel  |

# **Logic Symbol**

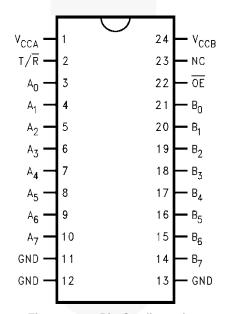

# **Pin Configuration**

Figure 2. Pin Configuration

# **Pin Definitions**

| Pin #                             | Name                                                                                                                                     | Description                      |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1                                 | V <sub>CCA</sub>                                                                                                                         | Supply Voltage                   |

| 2                                 | T/R                                                                                                                                      | Transmit/Receive Input           |

| 3, 4, 5, 6, 7, 8, 9, 10           | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> , A <sub>4</sub> ,<br>A <sub>5</sub> , A <sub>6</sub> , A <sub>7</sub> | Port-A Inputs or 3-State Outputs |

| 11, 12, 13                        | GND                                                                                                                                      | Ground                           |

| 14, 15, 16, 17, 18, 19,<br>20, 21 | B <sub>7</sub> , B <sub>6</sub> , B <sub>5</sub> , B <sub>4</sub> , B <sub>3</sub> ,<br>B <sub>2</sub> , B <sub>1</sub> , B <sub>0</sub> | Port-B Inputs or 3-State Outputs |

| 22                                | /OE                                                                                                                                      | Output Enable Input              |

| 23                                | NC                                                                                                                                       | No Connect                       |

| 24                                | V <sub>CCB</sub>                                                                                                                         | Supply Voltage                   |

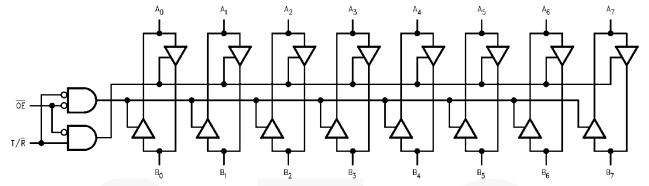

# **Logic Diagram**

Figure 3. Logic Diagram

Table 1. Truth Table

| Inp | outs | Outputs             |

|-----|------|---------------------|

| /OE | T/R  |                     |

| L   | L    | Bus B Data to Bus A |

| L   | Н    | Bus A Data to Bus B |

| Н   | X    | HIGH-Z State        |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                              | P                                       | arameter             |                  | Min. | Max.                     | Unit |

|-------------------------------------|-----------------------------------------|----------------------|------------------|------|--------------------------|------|

| V <sub>CCA</sub> , V <sub>CCB</sub> | Supply Voltage                          | Supply Voltage       |                  |      |                          | V    |

| V <sub>IN</sub>                     | DC Input Voltage; (/OE, T/R)            |                      |                  |      |                          | V    |

| V                                   | DC Input / Output Voltage               | A <sub>n</sub>       |                  |      |                          | V    |

| V <sub>I/O</sub>                    | DC Input / Output Voltage               |                      | Bn               | -0.5 | V <sub>CCB</sub> to +0.5 | V    |

| I <sub>IN</sub>                     | DC Input Diode Current (/OE and T/R)    |                      |                  |      | ±20                      | mA   |

| I <sub>OK</sub>                     | DC Output Diode Current                 |                      |                  |      | ±50                      | mA   |

| Io                                  | DC Output Source or Sink Curre          | nt                   |                  |      | ±50                      | mA   |

|                                     | Output Pin                              |                      |                  |      | ±50                      |      |

| I <sub>CC</sub> or I <sub>GND</sub> | DC V <sub>CC</sub> or Ground Current    | Maximum Cumant at    | I <sub>CCA</sub> |      | ±100                     | mA   |

|                                     |                                         | Maximum Current at   | I <sub>CCB</sub> |      | ±200                     |      |

| T <sub>STG</sub>                    | Storage Temperature Range               |                      |                  | -65  | +150                     | °C   |

| I <sub>SINK</sub>                   | DC Latch-Up Source or Sink Current      |                      |                  |      | ±300                     | mA   |

| TJ                                  | Maximum Junction Temperature Under Bias |                      |                  |      | +150                     | °C   |

| ESD                                 | Electrostatic Discharge<br>Capability   | Human Body Model, JE | SD22-A114        |      | 2500                     | V    |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol           | Parameter                                                                                                                |                | Min.             | Max.             | Unit |

|------------------|--------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------|

| $V_{CCA}$        | Cumply Voltage                                                                                                           |                | 2.7              | 3.6              | W    |

| V <sub>CCB</sub> | Supply Voltage                                                                                                           |                | 4.5              | 5.5              | V    |

| Vı               | Input Voltage (/OE and T/R)                                                                                              | 0              | V <sub>CCA</sub> | V                |      |

| V                | DC Input / Output Voltage                                                                                                | A <sub>n</sub> | 0                | V <sub>CCA</sub> | V    |

| $V_{I/O}$        | DC Input / Output Voltage                                                                                                | B <sub>n</sub> | 0                | V <sub>CCB</sub> | V    |

| T <sub>A</sub>   | Operating Temperature, Free Air                                                                                          |                | -40              | +85              | °C   |

| Δt / ΔV          | Minimum Input Edge Rate (V <sub>IN</sub> from 30 to 70% of V <sub>CC</sub> , V <sub>CC</sub> at 3.0 V, 4.5 V, and 5.5 V) |                |                  | 8                | ns/V |

#### Note:

1. Unused pins (inputs and I/O's) must be held HIGH or LOW. They may not float.

# **DC Electrical Characteristics**

| Comple ed        | Davama                                       | -1                     | Conditions                                                                                                                | V <sub>CCA</sub> | V <sub>CCB</sub> | T <sub>A</sub> = - | 25°C  | T <sub>A</sub> =-40 to+85°C | l lmita |

|------------------|----------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|------------------|--------------------|-------|-----------------------------|---------|

| Symbol           | Parame                                       | eter                   | Conditions                                                                                                                | (V)              | (V)              | Тур.               | Gua   | ranteed Limits              | Units   |

|                  |                                              | A <sub>n</sub> , T/R , |                                                                                                                           | 3.6              | 5.0              |                    | 2.0   | 2.0                         |         |

| $V_{IHA}$        | Minimum                                      | /OE                    | V <sub>OUT</sub> ≤ 0.1 V or                                                                                               | 2.7              | 5.0              |                    | 2.0   | 2.0                         |         |

|                  | HIGH Level<br>Input Voltage                  | _                      | ≥ V <sub>CC</sub> - 0.1 V                                                                                                 | 3.3              | 4.5              |                    | 2.0   | 2.0                         | V       |

| $V_{IHB}$        | p a v aag a                                  | B <sub>n</sub>         |                                                                                                                           | 3.3              | 5.5              |                    | 2.0   | 2.0                         |         |

|                  |                                              | A <sub>n</sub> , T/R , |                                                                                                                           | 3.6              | 5.0              |                    | 0.8   | 0.8                         |         |

| $V_{ILA}$        | Minimum                                      | /OE                    | V <sub>OUT</sub> ≤ 0.1 V or                                                                                               | 2.7              | 5.0              |                    | 0.8   | 0.8                         |         |

| \/               | LOW Level<br>Input Voltage                   | _                      | ≥ V <sub>CC</sub> - 0.1 V                                                                                                 | 3.3              | 4.5              |                    | 0.8   | 0.8                         | V       |

| $V_{ILB}$        | p a v aag a                                  | B <sub>n</sub>         |                                                                                                                           | 3.3              | 5.5              |                    | 0.8   | 0.8                         |         |

|                  |                                              |                        | I <sub>OUT</sub> =-100 μA                                                                                                 | 3.0              | 4.5              | 2.99               | 2.90  | 2.90                        |         |

|                  |                                              |                        | I <sub>OH</sub> =-24 mA                                                                                                   | 3.0              | 4.5              | 2.65               | 2.35  | 2.25                        |         |

| $V_{OHA}$        | Minimum HIG                                  | H Level                | I <sub>OH</sub> =-12 mA                                                                                                   | 2.7              | 4.5              | 2.50               | 2.30  | 2.20                        |         |

|                  | Output Voltag                                |                        | I <sub>OH</sub> =-24 mA                                                                                                   | 2.7              | 4.5              | 2.30               | 2.10  | 2.00                        | V       |

| /                |                                              |                        | Ι <sub>Ουτ</sub> =-100 μΑ                                                                                                 | 3.0              | 4.5              | 4.50               | 4.40  | 4.40                        |         |

| $V_{OHB}$        |                                              |                        | I <sub>OH</sub> =-24 mA                                                                                                   | 3.0              | 4.5              | 4.25               | 3.86  | 3.76                        |         |

|                  |                                              |                        | I <sub>OUT</sub> =100 μA                                                                                                  | 3.0              | 4.5              | 0.002              | 0.100 | 0.100                       |         |

| .,               |                                              |                        | I <sub>OH</sub> =24 mA                                                                                                    | 3.0              | 4.5              | 0.210              | 0.360 | 0.440                       | N .     |

| $V_{OLA}$        | Minimum LOV                                  | V Level                | I <sub>OH</sub> =12 mA                                                                                                    | 2.7              | 4.5              | 0.110              | 0.360 | 0.440                       |         |

|                  | Output Voltage                               |                        | I <sub>OH</sub> =24 mA                                                                                                    | 2.7              | 4.5              | 0.220              | 0.420 | 0.500                       | V       |

| .,               |                                              |                        | Ι <sub>Ουτ</sub> =100 μΑ                                                                                                  | 3.0              | 4.5              | 0.002              | 0.100 | 0.100                       |         |

| $V_{OLB}$        |                                              |                        | I <sub>OH</sub> =24 mA                                                                                                    | 3.0              | 4.5              | 0.180              | 0.360 | 0.440                       |         |

| I <sub>IN</sub>  | Maximum Inpl<br>Leakage Curr<br>/OE, T/R     |                        | V <sub>IN</sub> =V <sub>CCB</sub> , GND                                                                                   | 3.6              | 5.5              |                    | ±0.1  | ±1.0                        | μΑ      |

| I <sub>OZA</sub> | Maximum 3-S<br>Output Leaka                  |                        | V <sub>IN</sub> =V <sub>IL</sub> , V <sub>IH</sub> ;<br>/OE= V <sub>CCA</sub> ;<br>V <sub>O</sub> =V <sub>CCA</sub> , GND | 3.6              | 5.5              |                    | ±0.5  | ±5.0                        | μΑ      |

| I <sub>OZB</sub> | Maximum 3-S<br>Output Leaka                  |                        | V <sub>IN</sub> =V <sub>IL</sub> , V <sub>IH</sub> ;<br>/OE= V <sub>CCA</sub> ;<br>V <sub>O</sub> =V <sub>CCB</sub> , GND | 3.6              | 5.5              |                    | ±0.5  | ±5.0                        | μΑ      |

|                  | Maximum                                      | B <sub>n</sub>         | V <sub>IN</sub> =V <sub>CCB</sub> -2.1 V                                                                                  | 3.6              | 5.5              | 1.00               | 1.35  | 1.50                        |         |

| Δlcc             |                                              |                        | V <sub>IN</sub> =V <sub>CCA</sub> -0.6 V                                                                                  | 3.6              | 5.5              |                    | 0.35  | 0.50                        | mA      |

| I <sub>CCA</sub> | Quiescent V <sub>CCA</sub> Supply<br>Current |                        | $\begin{array}{l} A_n = V_{CCA} \text{ or GND,} \\ B_n = V_{CCB} \text{ or GND,} \\ /OE = GND, \\ T/R = GND \end{array}$  | 3.6              | 5.5              |                    | 5     | 50                          |         |

| I <sub>CCB</sub> | Quiescent V <sub>CCB</sub> Supply<br>Current |                        | A <sub>n</sub> =V <sub>CCA</sub> or GND,<br>B <sub>n</sub> =V <sub>CCB</sub> or GND,<br>/OE=GND,<br>T/R =V <sub>CCA</sub> | 3.6              | 5.5              |                    | 8     | 80                          | μА      |

Continued on the following page...

# **DC Electrical Characteristics** (Continued)

| Symbol            | Parameter                                                         | Conditions | V <sub>CCA</sub> | V <sub>CCB</sub> | T <sub>A</sub> = -25°C | T <sub>A</sub> =- | 40 to+85°C   | Units |  |

|-------------------|-------------------------------------------------------------------|------------|------------------|------------------|------------------------|-------------------|--------------|-------|--|

| Syllibol          | Farameter                                                         | Conditions | (V)              | (V)              | Тур.                   | Guara             | nteed Limits | Cinto |  |

| $V_{OLPA}$        | Quiet Output Maximum<br>Dynamic V <sub>OL</sub> <sup>(2, 3)</sup> |            | 3.3              | 5.0              |                        | 0.8               |              | V     |  |

| $V_{OLPB}$        | Dynamic V <sub>OL</sub> <sup>(2, 3)</sup>                         |            | 3.3              | 5.0              |                        | 1.5               |              | V     |  |

| $V_{OLVA}$        | Quiet Output Minimum                                              |            | 3.3              | 5.0              |                        | -0.8              |              | V     |  |

| $V_{OLVB}$        | Quiet Output Minimum<br>Dynamic V <sub>OL</sub> <sup>(2, 3)</sup> |            | 3.3              | 5.0              |                        | -1.2              |              | V     |  |

| $V_{IHDA}$        | Minimum HIGH Level                                                |            | 3.3              | 5.0              |                        | 2.0               |              |       |  |

| V <sub>IHDB</sub> | Dynamic Input<br>Voltage <sup>(2, 4)</sup>                        |            | 3.3              | 5.0              |                        | 2.0               |              | V     |  |

| V <sub>ILDA</sub> | Maximum LOW Level                                                 |            | 3.3              | 5.0              |                        | 0.8               |              |       |  |

| V <sub>ILDB</sub> | Dynamic Input<br>Voltage <sup>(2, 4)</sup>                        |            | 3.3              | 5.0              |                        | 0.8               |              | V     |  |

## Notes:

- Worst-case package.

- 3.

- Maximum number of outputs defined as (n). Data inputs are driven 0 V to  $V_{CC}$  level; one output at GND. Maximum number of data inputs (n) switching. (n-1) inputs switching 0 V to  $V_{CC}$  level. Input-under-test switching;  $V_{CC}$  level to threshold ( $V_{IHD}$ ), 0V to threshold ( $V_{ILD}$ ), f=1 MHz.

## **AC Electrical Characteristics**

| Symbol                                | Parameter                                                  | $T_A=+25^{\circ}C$ , $C_L=50$ pF, $V_{CCA}=3.3~V^{(5)}$ , $V_{CCB}=5.0~V^{(6)}$ |      | T <sub>A</sub> =-40 to<br>C <sub>L</sub> =50<br>V <sub>CCA</sub> =3<br>V <sub>CCB</sub> =5 | 0 pF,<br>.3 V <sup>(5)</sup> , | $T_A$ =-40 to +85°C,<br>$C_L$ =50 pF,<br>$V_{CCA}$ =2.7 V,<br>$V_{CCB}$ =5.0 V |      | Units |    |

|---------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------|------|-------|----|

|                                       |                                                            | Min.                                                                            | Тур. | Max.                                                                                       | Min.                           | Max.                                                                           | Min. | Max.  |    |

|                                       | Propagation                                                | 1.0                                                                             | 5.4  | 8.0                                                                                        | 1.0                            | 8.5                                                                            | 1.0  | 9.0   |    |

|                                       | Delay A to B                                               | 1.0                                                                             | 5.6  | 7.5                                                                                        | 1.0                            | 8.0                                                                            | 1.0  | 8.5   | ns |

| t <sub>PHL</sub> , t <sub>PLH</sub>   | Propagation<br>Delay B to A                                | 1.0                                                                             | 5.1  | 7.5                                                                                        | 1.0                            | 8.0                                                                            | 1.0  | 8.5   |    |

|                                       |                                                            | 1.0                                                                             | 5.7  | 7.5                                                                                        | 1.0                            | 8.0                                                                            | 1.0  | 8.5   |    |

|                                       | Output Enable<br>Time /OE to B                             | 1.0                                                                             | 4.8  | 8.0                                                                                        | 1.0                            | 8.5                                                                            | 1.0  | 9.0   |    |

|                                       |                                                            | 1.0                                                                             | 6.3  | 8.5                                                                                        | 1.0                            | 9.0                                                                            | 1.0  | 9.5   | no |

| $t_{PZL}, t_{PZH}$                    | Output Enable                                              | 1.0                                                                             | 6.3  | 8.5                                                                                        | 1.0                            | 9.0                                                                            | 1.0  | 9.5   | ns |

|                                       | Time /OE to A                                              | 1.0                                                                             | 6.8  | 9.0                                                                                        | 1.0                            | 9.5                                                                            | 1.0  | 10.0  |    |

|                                       | Output Disable                                             | 1.0                                                                             | 5.3  | 7.5                                                                                        | 1.0                            | 8.0                                                                            | 1.0  | 8.5   |    |

| /                                     | Time /OE to B                                              | 1.0                                                                             | 4.2  | 7.0                                                                                        | 1.0                            | 7.5                                                                            | 1.0  | 8.0   |    |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>   | Output Disable                                             | 1.0                                                                             | 5.3  | 8.0                                                                                        | 1.0                            | 8.5                                                                            | 1.0  | 9.0   | ns |

|                                       | Time /OE to A                                              | 1.0                                                                             | 3.7  | 6.5                                                                                        | 1.0                            | 7.0                                                                            | 1.0  | 7.5   |    |

| t <sub>OSHL</sub> , t <sub>OSLH</sub> | Output to Output<br>Skew, Data to<br>Output <sup>(7)</sup> |                                                                                 | 1.0  | 1.5                                                                                        |                                | 1.5                                                                            |      | 1.5   | ns |

#### Notes:

- 5. Voltage range 3.3 V is  $3.3 \text{ V} \pm 0.3 \text{ V}$ .

- 6. Voltage range 5.0 V is 5.0 V  $\pm$  0.5 V.

- 7. Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (toshl) or LOW-to-HIGH (toslh). Parameter guaranteed by design.

# Capacitance

| Symbol           | Parameter                                    | Conditions             | Тур.                                                  | Units |     |

|------------------|----------------------------------------------|------------------------|-------------------------------------------------------|-------|-----|

| C <sub>IN</sub>  | Input Capacitance                            | V <sub>CC</sub> = Open | 4.5                                                   | pF    |     |

| C <sub>I/O</sub> | Input / Output Capacitance                   |                        | V <sub>CCA</sub> = 3.3 V,<br>V <sub>CCB</sub> = 5.0 V | 15    | pF  |

|                  | Power Dissipation Conscitance (8)            | A to B                 | $V_{CCA} = 3.3 \text{ V},$                            | 55    | s E |

| CPD              | Power Dissipation Capacitance <sup>(8)</sup> |                        | $V_{CCB} = 5.0 \text{ V}$                             | 40    | pF  |

#### Note:

8. C<sub>PD</sub> is measured at 10 MHz.

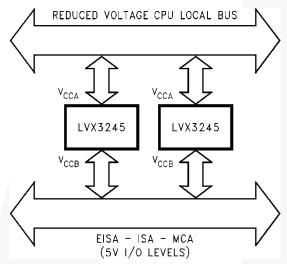

## 8-Bit Dual-Supply Translating Transceiver

The 74LVX3245 is a dual-supply device capable of bidirectional signal translation. This level shifting ability provides an efficient interface between low-voltage CPU local bus with memory and a standard bus defined by 5 V I/O levels. The device control inputs can be controlled by the low-voltage CPU and core logic or a bus arbitrator with 5 V I/O levels.

Manufactured on a sub-micron CMOS process, the 74LVX3245 is ideal for mixed voltage applications such as notebook computers using 3.3 V CPUs and 5 V peripheral devices.

Figure 4. Application Example

## **Power-Up Considerations**

To ensure that the system does not experience unnecessary I<sub>CC</sub> current draw, bus contention, or oscillations during power up; the following guidelines should be followed to *(refer to Table 2)*:

- Power up the control side of the device first (V<sub>CCA</sub>).

- /OE should ramp with or ahead of V<sub>CCA</sub>. This helps guard against bus contention.

- The Transmit/Receive (T/R) control pin should ramp with V<sub>CCA</sub>. This ensures that the A-port data pins are configured as inputs. With V<sub>CCA</sub> receiving power first, the I/O port should be configured as an input to help guard against bus contention and oscillations.

- A-side data inputs should be driven to a valid logic level. This prevents excessive current draw.

The above steps ensure that there are no bus contentions or oscillations, and therefore no excessive current draw occurs during the power-up cycling. These steps help prevent possible damage to the translator devices and potential damage to other system components.

Table 2. Low Voltage Translator Power-Up Sequencing

| Device    | V <sub>CCA</sub>        | V <sub>CCB</sub>    | T/R                           | /OE                           | A-Side I/O                    | B-Side I/O | Floatable<br>Pin Allowed |

|-----------|-------------------------|---------------------|-------------------------------|-------------------------------|-------------------------------|------------|--------------------------|

| 74LVX3245 | 3 V<br>(Power-Up First) | 5 V<br>Configurable | Ramp<br>with V <sub>CCA</sub> | Ramp<br>with V <sub>CCA</sub> | Logic 0 V or V <sub>CCA</sub> | Outputs    | No                       |

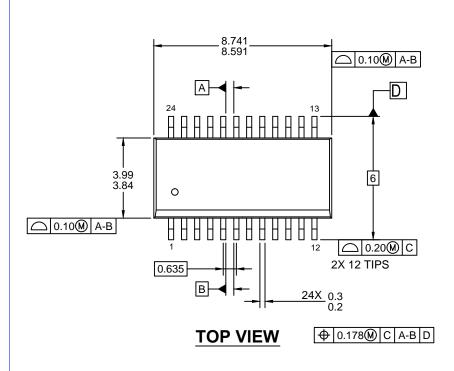

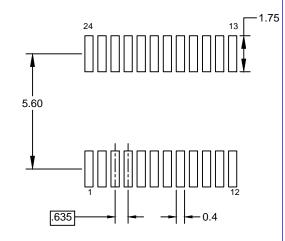

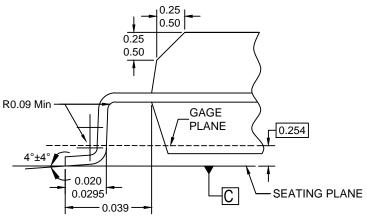

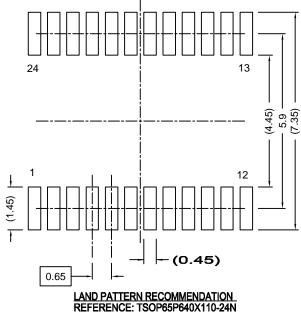

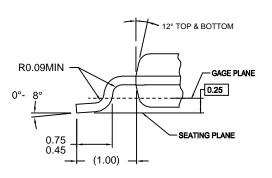

# LAND PATTERN RECOMMENDATION

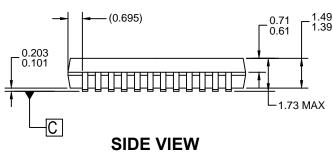

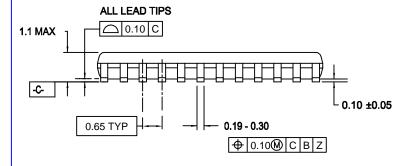

# END VIEW

## NOTES:

- A. THIS PACKAGE CONFORMS TO JEDEC M0-137 VARIATION AE

- **B. ALL DIMENSIONS ARE IN MILLIMETERS**

- C. DIMENSIONING AND TOLERANCES PER ANSI Y14.5M, 2009.

- D. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS

- E. LAND PATTERN STANDARD: SOP63P600X175-24M.

- F. DRAWING FILE NAME: MKT-MQA24rev3

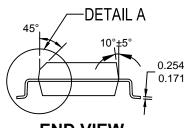

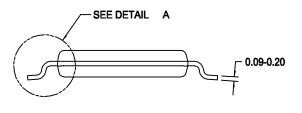

## **DETAIL A**

| REVISIONS |                                                                          |               |            |          |  |

|-----------|--------------------------------------------------------------------------|---------------|------------|----------|--|

| LTR       | DESCRIPTION                                                              | EDCN          | DATE       | BY/APP'D |  |

|           | CHANGE TO FSPM DRAWING FORMAT<br>N LEAD SHIFT TOL. FROM 0.13MM TO 0.10MM | ECN-MTC24REV4 | 21/12/2006 | H.ALLEN  |  |

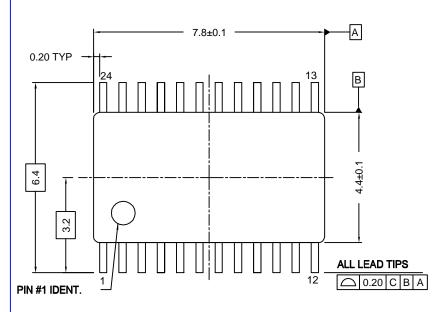

## DIMENSIONS ARE IN MILLIMETERS

### **NOTES:**

- A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AD, DATE 10/97.

- **B. DIMENSIONS ARE IN MILLIMETERS.**

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M, 1994

- E. DRAWING FILE NAME: MTC24REV4

MTC24REV4

**DETAIL** A

| APPROVALS PRAWN FEITAN         | <b>DATE</b><br>8-10-99        | FAIRC      |  | Dayan      | ı Lepas, FIZ,<br>, Penang, Malaysia |  |

|--------------------------------|-------------------------------|------------|--|------------|-------------------------------------|--|

| DFTG. CHK.  H.ALLEN ENGR. CHK. | 21-12-2006                    |            |  |            |                                     |  |

| PROJECTIO                      | SCALE<br>N/A                  | SIZE<br>A4 |  |            |                                     |  |

| INCH                           | DO NOT SCALE DRAWING SHEET 10 |            |  | SHEET 1 of | 1                                   |  |

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

$\begin{array}{lll} \mathsf{AccuPower^{\mathsf{TM}}} & \mathsf{F-PFS^{\mathsf{TM}}} \\ \mathsf{AttitudeEngine^{\mathsf{TM}}} & \mathsf{FRFET}^{\texttt{®}} \end{array}$

Awinda<sup>®</sup> Global Power Resource SM

AX-CAP®\* GreenBridge™

BitSiC™ Green FPS™

Build it Now™ Green FPS™ e-Series™

Current Transfer Logic™ Making Small Speakers Sound Louder

DEUXPEED® and Better™

Dual Cool™ MegaBuck™

EcoSPARK® MICROCOUPLER™

EfficientMax™ MicroFET™

EfficientMax™ MicroFET™

ESBC™ MicroPak™

MicroPak™

MicroPak2™

Fairchild® MillerDrive™

MotionMax™

Fairchild Semiconductor®

Farchild Semiconductor

FACT Quiet Series™

FACT®

FastvCore™

FETBench™

FPS™

MotionGrid®

MTI®

MTX®

MVN®

FETBench™

MVN®

FPS™

OptoHiT™

OPTOLOGIC®

OPTOPLANAR®

Power Supply WebDesigner™ PowerTrench®

PowerXS™

Programmable Active Droop™ OFFT®

QS™ Quiet Series™ RapidConfigure™

T TM

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM®

STEALTH™

SuperFET®

SuperSOT™-3

SuperSOT™-6

SuperSOT™-8

SupreMOS®

SyncFET™

Sync-Lock™

SYSTEM GENERAL®'

TinyBoost®

TinyBuck®

TinyCalc™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPWM™

TinyPWM™

TranSiC™

TriFault Detect™

TRUECURRENT®\*\*

uSerDes™

SerDes"

UHC<sup>®</sup>

Ultra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

XS™

XS™

仙童®

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR WEBSITE AT <a href="http://www.fairchildsemi.com">http://www.fairchildsemi.com</a>, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### AUTHORIZED USE

Unless otherwise specified in this data sheet, this product is a standard commercial product and is not intended for use in applications that require extraordinary levels of quality and reliability. This product may not be used in the following applications, unless specifically approved in writing by a Fairchild officer: (1) automotive or other transportation, (2) military/aerospace, (3) any safety critical application – including life critical medical equipment – where the failure of the Fairchild product reasonably would be expected to result in personal injury, death or property damage. Customer's use of this product is subject to agreement of this Authorized Use policy. In the event of an unauthorized use of Fairchild's product, Fairchild accepts no liability in the event of product failure. In other respects, this product shall be subject to Fairchild's Worldwide Terms and Conditions of Sale, unless a separate agreement has been signed by both Parties.

#### **ANTI-COUNTERFEITING POLICY**

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Terms of Use

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Definition of Terms      |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 177