### FT1124/FT1125

Dual/Quad Low Noise, High Speed Precision Op Amps

### **Features**

■ 100% Tested Low Voltage Noise: 2.7nV/√Hz Typ 4.2nV/√Hz Max

■ Slew Rate: 4.5V/µs Typ

Gain Bandwidth Product: 12.5MHz Typ

Offset Voltage, Prime Grade: 70µV Max

Low Grade: 100µV Max

■ High Voltage Gain: 5 Million Min

Supply Current Per Amplifier: 2.75mA Max

Common Mode Rejection: 112dB Min

Power Supply Rejection: 116dB Min

■ Available in 8-Pin SO Package

### **Applications**

Two and Three Op Amp Instrumentation Amplifiers

■ Low Noise Signal Processing

Active Filters

Microvolt Accuracy Threshold Detection

Strain Gauge Amplifiers

Direct Coupled Audio Gain Stages

■ Tape Head Preamplifiers

Infrared Detectors

### **Description**

The FT1124 dual and FT1125 quad are high performance op amps that offer higher gain, slew rate and bandwidth than the industry standard OP-27 and competing OP-270/OP-470 op amps. In addition, the FT1124/FT1125 have lower  $I_B$  and  $I_{OS}$  than the OP-27; lower  $V_{OS}$  and noise than the OP-270/OP-470.

In the design, processing and testing of the device, particular attention has been paid to the optimisation of the entire distribution of several key parameters. Slew rate, gain bandwidth and 1kHz noise are 100% tested for each individual amplifier. Consequently, the specifications of even the lowest cost grades (the FT1124C and the FT1125C) have been spectacularly improved compared to equivalent grades of competing amplifiers.

Power consumption of the FT1124 is one half of two OP-27s. Low power and high performance in an 8-pin SO package make the FT1124 a first choice for surface mounted systems and where board space is restricted.

For a decompensated version of these devices, with three times higher slew rate and bandwidth, please see the FT1126/FT1127 data sheet.

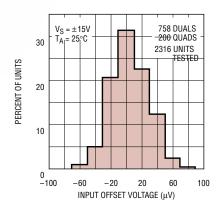

# Input Offset Voltage Distribution (All Packages, FT1124 and FT1125)

### Absolute Maximum Ratings (Note 1)

| Supply Voltage                      | ±22V                  |

|-------------------------------------|-----------------------|

| Input Voltages Equ                  | ual to Supply Voltage |

| Output Short-Circuit Duration       | Indefinite            |

| Differential Input Current (Note 6) | ±25mA                 |

| Lead Temperature (Soldering, 10 se  | ec)300°C              |

| Storage Temperature Range           | 65°C to 150°C         |

Operating Temperature Range FT1124AC/FT1124C FT1125AC/FT1125C (Note 10) ...... -40°C to 85°C FT1124AI/FT1124I ...... -40°C to 85°C FT1124AM/FT1124M FT1125AM/FT1125M ...... -55°C to 125°C

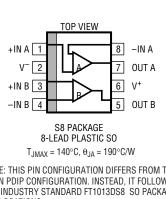

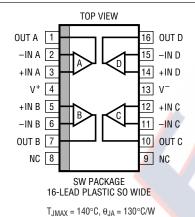

NOTE: THIS PIN CONFIGURATION DIFFERS FROM THE 8-PIN PDIP CONFIGURATION. INSTEAD, IT FOLLOWS THE INDUSTRY STANDARD FT1013DS8 SO PACKAGE PIN LOCATIONS

ORDER PART

**NUMBER**

1124AI 11241

J8 PACKAGE 8-LEAD CERAMIC DIP  $T_{JMAX} = 160^{\circ}C$ ,  $\theta_{JA} = 100^{\circ}C/W$

FT1124CJ8 FT1124AMJ8 FT1124MJ8

FT1125CSW

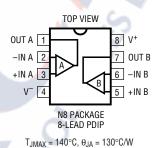

$T_{JMAX} = 140^{\circ}C$ ,  $\theta_{JA} = 110^{\circ}C/W$  (N)

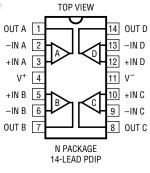

J PACKAGE 14-LEAD CERAMIC DIP  $T_{JMAX} = 160^{\circ}C$ ,  $\theta_{JA} = 80^{\circ}C/W$  FT1125ACN FT1125CN

FT1125CJ FT1125AMJ FT1125MJ

## **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ , unless otherwise noted.

| SYMBOL                              | PARAMETER                                   | CONDITIONS (Note 2)                                                       |        | FT1124AC/AI/AM<br>FT1125AC/AM |            |            | FT1124C/I/M<br>FT1125C/M |            |                   |

|-------------------------------------|---------------------------------------------|---------------------------------------------------------------------------|--------|-------------------------------|------------|------------|--------------------------|------------|-------------------|

|                                     |                                             |                                                                           | MIN    | TYP                           | MAX        | MIN        | TYP                      | MAX        | UNITS             |

| V <sub>OS</sub>                     | Input Offset Voltage                        | FT1124<br>FT1125                                                          |        | 20<br>25                      | 70<br>90   |            | 25<br>30                 | 100<br>140 | μV<br>μV          |

| $\frac{\Delta V_{OS}}{\Delta Time}$ | Long-Term Input Offset<br>Voltage Stability |                                                                           |        | 0.3                           |            |            | 0.3                      |            | μV/Mo             |

| I <sub>OS</sub>                     | Input Offset Current                        | FT1124<br>FT1125                                                          |        | 5<br>6                        | 15<br>20   | 9          | 6<br>7                   | 20<br>30   | nA<br>nA          |

| $I_{B}$                             | Input Bias Current                          |                                                                           |        | ±7                            | ±20        |            | ±8                       | ±30        | nA                |

| e <sub>n</sub>                      | Input Noise Voltage                         | 0.1Hz to 10Hz (Notes 8, 9)                                                |        | 70                            | 200        | 1          | 70                       |            | nV <sub>P-P</sub> |

|                                     | Input Noise Voltage Density                 | f <sub>0</sub> = 10Hz (Note 5)<br>f <sub>0</sub> = 1000Hz (Note 3)        |        | 3.0<br>2.7                    | 5.5<br>4.2 |            | 3.0<br>2.7               | 5.5<br>4.2 | nV/√Hz<br>nV/√Hz  |

| i <sub>n</sub>                      | Input Noise Current Density                 | f <sub>0</sub> = 10Hz<br>f <sub>0</sub> = 1000Hz                          |        | 1.3<br>0.3                    | 7          |            | 1.3<br>0.3               |            | pA/√Hz<br>pA/√Hz  |

| $V_{CM}$                            | Input Voltage Range                         |                                                                           | ±12    | ±12.8                         |            | ±12        | ±12.8                    |            | V                 |

| CMRR                                | Common Mode Rejection Ratio                 | V <sub>CM</sub> = ±12V                                                    | 112    | 126                           |            | 106        | 124                      |            | dB                |

| PSRR                                | Power Supply Rejection Ratio                | $V_S = \pm 4V \text{ to } \pm 18V$                                        | 116    | 126                           |            | 110        | 124                      |            | dB                |

| A <sub>VOL</sub>                    | Large-Signal Voltage Gain                   | $R_L \ge 10k$ , $V_{OUT} = \pm 10V$<br>$R_L \ge 2k$ , $V_{OUT} = \pm 10V$ | 5<br>2 | 17<br>4                       |            | 3.0<br>1.5 | 15<br>3                  |            | V/μV<br>V/μV      |

| $\overline{V_{OUT}}$                | Maximum Output Voltage Swing                | $R_L \ge 2k$                                                              | ±13    | ±13.8                         |            | ±12.5      | ±13.8                    |            | V                 |

| SR                                  | Slew Rate                                   | $R_L \ge 2k$ (Notes 3, 7)                                                 | 3      | 4.5                           |            | 2.7        | 4.5                      |            | V/µs              |

| GBW                                 | Gain Bandwidth Product                      | f <sub>0</sub> = 100kHz (Note 3)                                          | 9      | 12.5                          |            | 8          | 12.5                     |            | MHz               |

| $\overline{Z_0}$                    | Open-Loop Output Resistance                 | $V_{OUT} = 0$ , $I_{OUT} = 0$                                             | 4      | 75                            |            |            | 75                       |            | Ω                 |

| Is                                  | Supply Current per Amplifier                |                                                                           |        | 2.3                           | 2.75       |            | 2.3                      | 2.75       | mA                |

|                                     | Channel Separation                          | $f \le 10$ Hz (Note 9)<br>V <sub>OUT</sub> = ±10V, R <sub>L</sub> = 2k    | 134    | 150                           |            | 130        | 150                      |            | dB                |

### The ullet denotes the specifications which apply over the $-55^{\circ}C \leq T_A \leq 125^{\circ}C$ temperature range, $V_S = \pm 15V$ , unless otherwise noted.

| SYMBOL                              | PARAMETER                             |                                     |   | FT1124AM<br>FT1125AM |       |      | FT1124M<br>FT1125M |       |      |       |

|-------------------------------------|---------------------------------------|-------------------------------------|---|----------------------|-------|------|--------------------|-------|------|-------|

|                                     |                                       | CONDITIONS (Note 2)                 |   | MIN                  | TYP   | MAX  | MIN                | TYP   | MAX  | UNITS |

| V <sub>OS</sub>                     | Input Offset Voltage                  | FT1124                              | • |                      | 50    | 170  |                    | 60    | 250  | μV    |

|                                     |                                       | FT1125                              | • |                      | 55    | 190  |                    | 70    | 290  | μV    |

| $\frac{\Delta V_{OS}}{\Delta Temp}$ | Average Input Offset<br>Voltage Drift | (Note 5)                            | • |                      | 0.3   | 1.0  |                    | 0.4   | 1.5  | μV/°C |

| I <sub>OS</sub>                     | Input Offset Current                  | FT1124                              | • |                      | 18    | 45   |                    | 20    | 60   | nA    |

| 00                                  |                                       | FT1125                              | • |                      | 18    | 55   |                    | 20    | 70   | nA    |

| I <sub>B</sub>                      | Input Bias Current                    |                                     | • |                      | ±18   | ±55  |                    | ±20   | ±70  | nA    |

| $V_{CM}$                            | Input Voltage Range                   |                                     | • | ±11.3                | ±12   |      | ±11.3              | ±12   |      | V     |

| CMRR                                | Common Mode Rejection Ratio           | $V_{CM} = \pm 11.3V$                | • | 106                  | 122   |      | 100                | 120   |      | dB    |

| PSRR                                | Power Supply Rejection Ratio          | $V_S = \pm 4V \text{ to } \pm 18V$  | • | 110                  | 122   |      | 104                | 120   |      | dB    |

| A <sub>VOL</sub>                    | Large-Signal Voltage Gain             | $R_L \ge 10k$ , $V_{OUT} = \pm 10V$ | • | 3                    | 10    |      | 2.0                | 10    |      | V/µV  |

|                                     |                                       | $R_L \ge 2k$ , $V_{OUT} = \pm 10V$  | • | 1                    | 3     |      | 0.7                | 2     |      | V/µV  |

| V <sub>OUT</sub>                    | Maximum Output Voltage Swing          | $R_L \ge 2k$                        | • | ±12.5                | ±13.6 |      | ±12                | ±13.6 |      | V     |

| SR                                  | Slew Rate                             | $R_L \ge 2k \text{ (Notes 3, 7)}$   | • | 2.3                  | 3.8   |      | 2                  | 3.8   |      | V/µs  |

| I <sub>S</sub>                      | Supply Current per Amplifier          |                                     | • |                      | 2.5   | 3.25 |                    | 2.5   | 3.25 | mA    |

Ashley Crt, Henley, Marlborough, Wilts, SN8 3RH UK

Tel: +44(0)1264 731200 Fax:+44(0)1264 731444

E-mail

info@forcetechnologies.co.uk tech@forcetechnologies.co.uk sales@forcetechnologies.co.uk

www.forcetechnologies.co.uk

Unless otherwise stated in this SCD/Data sheet, Force Technologies Ltd reserve the right to make changes, without notice, in the products, Includ -ing circuits, cells and/or software, described or contained herein in order to improve design and/or performance. Force Technologies resumes no responsibility or liability for the use of any of these products, conveys no licence or any title under patent, copyright, or mask work to these products, and makes no representation or warranties that that these products are free from patent, copyright or mask work infringement, unless otherwise specified.

#### **Life Support Applications**

Force Technologies products are not designed for use in life support appliances, devices or systems where malfunction of a Force Technologies product can reasonably be expected to result in a personal injury. Force Technologies customers using or selling Force Technologies products for use in such applications do so at their own risk and agree to fully indemnify Force Technologies for any damages resulting from such improper use or sale.

All trademarks acknowledged

Copyright Force Technologies Ltd 2007

Click here to request full data sheet