#### OBJECTIVE SPECIFICATIONS

### Features

- 8-Bit parallel-out storage register performs serial-to-parallel conversion with storage

- Asynchronous parallel clear

- Active high decoder

- Enable/Disable input simplifies expansion

- Expandable for N-bit applications

- Four distinct functional modes

- Function, pin-out, speed and drive compatability with 54/74LS logic family

- Low power consumption characteristic of CMOS

- High-Drive-Current outputs:  $I_{oL} = 8 \text{ mA } @ V_{oL} = 0.5V$

- Inputs and outputs interface directly with TTL, NMOS and CMOS devices

- Wide operating voltage range: 4.5V to 5.5V

- Characterized for operation over industial and military temperature ranges:

74HCTLS: -40°C to +85°C 54HCTLS: -55°C to +125°C

### Function Table

| Inputs<br>CLR G |   | Output of<br>Addressed<br>Latch | Each<br>Other<br>Output | Function             |  |

|-----------------|---|---------------------------------|-------------------------|----------------------|--|

| H               | L | D                               | Q <sub>j</sub> ,        | Addressable Latch    |  |

| H               | H | Q <sub>i</sub> ,                | Q <sub>j</sub> ,        | Memory               |  |

| L               | L | D                               | L                       | 8-Line Demultiplexer |  |

| L               | H | L                               | L                       | Clear                |  |

D = the level at the data input.

$Q_{io}$  = the level of  $Q_i$  (i = Q, i, ... 7, as appropriate) before indicated steady-state input conditions were established.

### 8-Bit Addressable Latches

### Description

The '259 is a high-speed addressable latch designed for general purpose storage applications in digital systems. It can be used for implementing working registers, serial-holding registers and active-high decoders or demultiplexers.

The '259 has four distinct modes of opration that are selected via the clear ( $\overline{CLR}$ ) and enable ( $\overline{G}$ ) inputs:

1) addressable latch; 2) memory; 3) active-high eight-channel demultiplexer; and 4) clear.

In the addressable latch mode, data on the data input (D) is written into the addressed latch. In this mode, data will be written into the addressed latch with all non-addressed latches remaining in their previous states.

In the memory mode, all latches remain in their previous state and are unavvected by the data or address inputs.

In the demultiplexing mode, addressed outputs will follow the state of the D input and all other outputs will remain low.

In the clear mode, all outputs are low and unaffected by the address and data inputs.

Fabrication using ISI proprietary ICE-MOS process, these devices provide speeds and drive capability equivalent to their LSTTL counterparts and yet maintain CMOS power levels. The input and output voltage levels allow direct interface with TTL, NMOS and CMOS devices without any external components.

All inputs and outputs are protected from damage due to static discharge by internal diode clamps to  $V_{\rm cc}$  and ground.

### Latch Selection Table

| S2          | Select Inputs<br>SI | S0 | Latch<br>Addressed |  |

|-------------|---------------------|----|--------------------|--|

| L           | L                   |    | 0                  |  |

| L<br>L<br>L | L                   | H  | 1                  |  |

| L           | H                   | L  | 2                  |  |

| L           | H                   | H  | 3                  |  |

| H           | L                   | L  | 4                  |  |

| H           | L                   | H  | 5                  |  |

| H           | H                   | L  | 6                  |  |

| H           | Н                   | H  | 7                  |  |

Pin Configuration

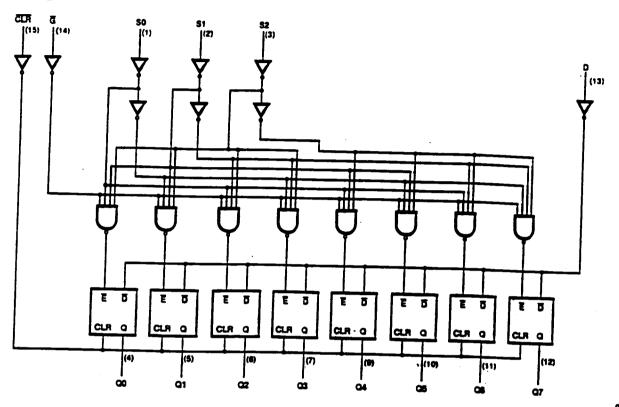

### Logic Diagram

## Absolute Maximum Ratings\*

| Supply Voltage Range, V <sub>cc</sub> 05V to 7V                |

|----------------------------------------------------------------|

| DC Input Diode Current, I,,                                    |

| $(V_1 < 0.5V \text{ or } V_1 > V_{cc} + 0.5V) \dots \pm 20mA$  |

| DC Output Diode Current, Iox                                   |

| $(V_o < -0.5V \text{ or } V_o > V_{cc} + 0.5V) \dots \pm 20mA$ |

| Continuous Output Current Per Pin, Io                          |

| $(-0.5V < V_o < V_{cc} + 0.5V) \dots + 35mA$                   |

| Continuous Current Through                                     |

| $V_{cc}$ or GND pins $\pm 125$ mA                              |

| Storage Temperature                                            |

| Range, T <sub>STG</sub> 65°C to +150°C                         |

| Power Dissipation Per Package, P 500mW                         |

\*Absolute Maximum Ratings are those values beyond which permanent damage to the device may occur. These are stress ratings only and functional operation of the device at or beyond them is not implied. Long exposure to these conditions may affect device reliability.

•Power Dissipation temperature derating: Plastic Package (N): -12 mW/°C from 65°C to 85°C Ceramic Package (J): -12 mW/°C from 100°C to 125°C

## Recommended Operating Conditions

Supply Voltage,  $V_{cc}$  ......4.5V to 5.5V DC Input & Output Voltages\*,  $V_{\rm IN}$ ,  $V_{\rm OUT}$  .....0V to  $V_{\rm CC}$  Operating Temperature

Range 74HCTLS: -40°C to +85,C 54HCTLS: -55°C to +125°C

\*Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{cc}$  or GND)

# DC Electrical Characteristics ( $V_{cc} = 5V \pm 10\%$ Unless Otherwise Specified)

| Sym                   | Parameter                            | Test Conditions                                                                 |                        |                               | $74HCTLS$ $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                              |    |

|-----------------------|--------------------------------------|---------------------------------------------------------------------------------|------------------------|-------------------------------|---------------------------------------------------------|------------------------------|----|

| $V_{IH}$              | Minimum High-Level                   | !                                                                               | Тур                    | 2.0                           | Guaranteed 2.0                                          | Guaranteed Limits 2.0 2.0    |    |

|                       | Input Voltage                        |                                                                                 |                        | <u></u>                       |                                                         |                              | V  |

| <i>V<sub>IL</sub></i> | Maximum Low-Level<br>Input Voltage   |                                                                                 |                        | 0.8                           | 0.8                                                     | 0.8                          | V  |

| V <sub>OH</sub>       | Minimum High-Level<br>Output Voltage | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_O = -20 \mu A$ $I_O = -4 \text{ mA}$    | V <sub>cc</sub><br>4.2 | V <sub>cc</sub> - 0.1<br>3.98 | V <sub>cc</sub> - 0.1<br>3.84                           | V <sub>cc</sub> - 0.1<br>3.7 | v  |

| V <sub>OL</sub>       | Maximum Low-Level<br>Output Voltage  | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_O = 20 \mu A$ $I_O = 4 mA$ $I_O = 8 mA$ | 0                      | 0.1<br>0.26<br>0.39           | 0.1<br>0.33<br>0.5                                      | 0.1<br>0.4                   | V  |

| I <sub>IN</sub>       | Maximum Input<br>Current             | $V_{iN} = V_{cc} \text{ or } GND$                                               |                        | ±0.1                          | ±1.0                                                    | ±1.0                         | μΑ |

| $I_{cc}$              | Maximum Quiescent                    | $V_{iN} = V_{cc} \text{ or } GND$                                               |                        | 8.0                           | 80.0                                                    | 160.0                        |    |

|                       | Supply Current                       | $I_{OUT} = 0 \ \mu A$                                                           |                        | ł                             |                                                         | 1                            | μΑ |

## AC Electrical Characteristics (Input t, , $t_f \le 6$ ns), HCTLS259

| Sym              | Param                                                                                                                        | eter        | Conditions •  |    | = 25°C<br>C - 5.0V | $74HCTLS$ $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{cc} = 5.0V \pm 10\%$ $Guaranteed$ | $T_A = -55 C to + 125 C$ $V_{CC} = 5.0V \pm 10\%$ Limits | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|----|--------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------|------|

| t <sub>PHL</sub> | Maximum Propagation Delay, CLR to any Q                                                                                      |             | $C_L = 50 pF$ | 22 | 30                 | 37                                                                                            | 45                                                       | ns   |

| $t_{PLH}$        | Maximum Propagation Delay, Data to any Q  Maximum Propagation Delay, Address to any Q  Maximum Propagation Delay, G to any Q |             |               | 20 | 27                 | 34                                                                                            | 41                                                       | ns   |

| t <sub>PHL</sub> |                                                                                                                              |             |               | 20 | 27                 | 34                                                                                            | 41                                                       |      |

| $t_{PLH}$        |                                                                                                                              |             |               | 26 | 34                 | 43                                                                                            | 51                                                       | ns   |

| $t_{PHL}$        |                                                                                                                              |             |               | 26 | 34                 | 43                                                                                            | 51                                                       |      |

| t <sub>PLH</sub> |                                                                                                                              |             |               | 22 | 30                 | 37                                                                                            | 45                                                       | ns   |

| t <sub>PHL</sub> |                                                                                                                              |             |               | 22 | 30                 | 37                                                                                            | 45                                                       |      |

|                  | Minimum<br>Pulse                                                                                                             | CLR Low     |               | 8  | 10                 | 13                                                                                            | 15                                                       |      |

| t,               | Width                                                                                                                        | $ar{G}$ Low |               | 8  | 10                 | 13                                                                                            | 15                                                       | ns   |

| t <sub>su</sub>  | Minimum Setup<br>Time,<br>Data or Address<br>before G↑                                                                       |             |               | 8  | 10                 | 13                                                                                            | 15                                                       | us   |

| t <sub>h</sub>   | Minimum Hold<br>Time,<br>Data or Address<br>after G↑                                                                         |             |               | 0  | 0                  | 0                                                                                             | o                                                        | ns   |

| C <sub>IN</sub>  | Maximum Input<br>Capacitance                                                                                                 |             | *             | 5  |                    |                                                                                               |                                                          | рF   |

| CPD              | Power Dissipation<br>Capacitance*                                                                                            |             |               | 80 |                    |                                                                                               |                                                          | pF   |

<sup>\*</sup> $C_{PD}$  determines the no-load dynamic power consumption:  $P_D = C_{PD} \ V_{CC}^2 \ f + I_{CC} \ V_{CC}$ • For AC switching test circuits and timing waveforms see section 2.