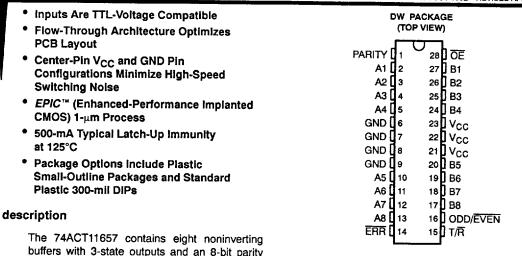

## 74ACT11657 OCTAL TRANSCEIVER WITH PARITY GENERATOR/CHECKER AND 3-STATE OUTPUTS

AUGUST 1992 - REVISED APRIL 1993

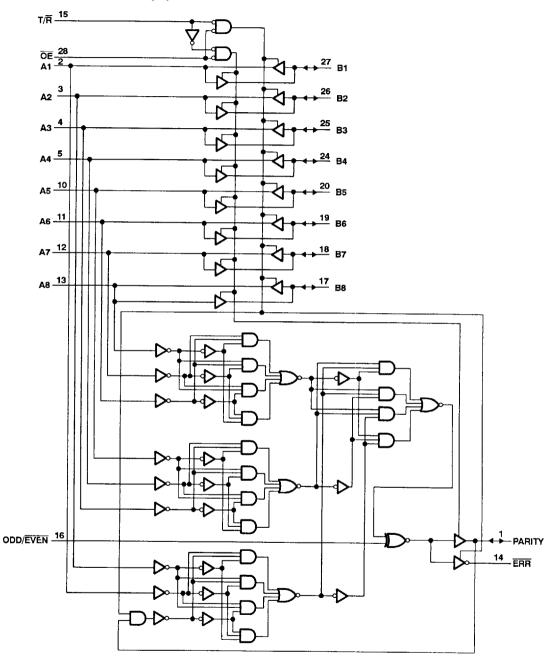

The transmit/receive  $(T/\overline{R})$  input determines the direction of data flow through the bidirectional transceivers. When  $T/\overline{R}$  is high, data flows from the A port to the B port (transmit mode); when  $T/\overline{R}$  is low, data flows from the B port to the A port (receive mode). When the output-enable  $(\overline{OE})$  input is high, both the A and B ports are in the high-impedance state.

Odd or even parity is selected by a logic high or low level, respectively, on the ODD/EVEN input. PARITY carries the parity bit value; it is an output from the parity generator/checker in the transmit mode and an input to the parity generator/checker in the receive mode.

In the transmit mode, after the A bus is polled to determine the number of high bits, PARITY is set to the logic level that maintains the parity sense selected by the level at the ODD/EVEN input. For example, if ODD/EVEN is low (even parity selected) and there are five high bits on the A bus, then PARITY is set to the logic high level so that an even number of the nine total bits (eight A-bus bits plus parity bit) are high.

In the receive mode, after the B bus is polled to determine the number of high bits, the  $\overline{\text{ERR}}$  output logic level indicates whether or not the data to be received exhibits the correct parity sense. For example, if  $\overline{\text{ODD/EVEN}}$  is high (odd parity selected), PARITY is high, and there are three high bits on the B bus, then  $\overline{\text{ERR}}$  is low, indicating a parity error.

The 74ACT11657 is characterized for operation from -40°C to 85°C.

generator/checker and is intended for bus-

oriented applications.

EPIC is a trademark of Texas Instruments Incorporated.

Texas V Instruments

# 74ACT11657 OCTAL TRANSCEIVER WITH PARITY GENERATOR/CHECKER AND 3-STATE OUTPUTS AUGUST 1992 - REVISED APRIL 1993

|  | ON |  |  |

|--|----|--|--|

|  |    |  |  |

|  |    |  |  |

| NUMBER OF A OR B     | INPUTS |     |          | INPUT/OUTPUT |     | OUTPUTS     |  |  |

|----------------------|--------|-----|----------|--------------|-----|-------------|--|--|

| INPUTS THAT ARE HIGH | ŌĒ     | T/R | ODD/EVEN | PARITY       | ERR | OUTPUT MODE |  |  |

| <u> </u>             | L      | Н   | Н        | Н            | Z   | Transmit    |  |  |

|                      | L      | н   | L        | L            | z   | Transmit    |  |  |

|                      | L      | L   | н        | н            | Н   | Receive     |  |  |

| 0, 2, 4, 6, 8        | L      | L   | н        | L            | L   | Receive     |  |  |

|                      | L      | L   | L        | н            | L   | Receive     |  |  |

|                      | L      | L   | L        | L            | н   | Receive     |  |  |

| <u>-,,,,,,,,,, </u>  | L      | Н   | Н        | L            | Z   | Transmit    |  |  |

|                      | L      | н   | L        | н            | z   | Transmit    |  |  |

|                      | L      | L   | н        | н            | L   | Receive     |  |  |

| 1, 3, 5, 7           | L      | L   | н        | L            | н   | Receive     |  |  |

|                      | L      | L   | L        | н            | н   | Receive     |  |  |

|                      | L      | L   | L        | L            | L   | Receive     |  |  |

| Don't care           | н      | ×   | X        | Z            | Z   | Z           |  |  |

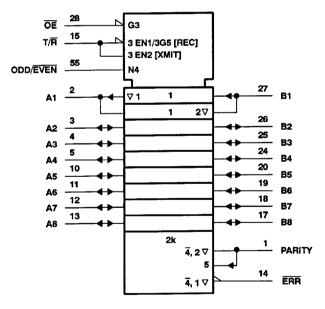

## logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

## logic diagram (positive logic)

AUGUST 1992 - REVISED APRIL 1993

## operating characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C

| PARAMETER |          |                                               |                  | TEST CONDITIONS         |                       | TYP | UNIT |

|-----------|----------|-----------------------------------------------|------------------|-------------------------|-----------------------|-----|------|

| 上         |          | Power dissipation capacitance per transceiver | Outputs enabled  | C <sub>1</sub> = 50 pF, | C( = 50 pF. f = 1 MHz | 95  | ρF   |

| 10        | pd Power |                                               | Outputs disabled | O[ 2 30 pr, 1 = 1       | 1 = 1 101112          | 21  | P'   |

#### PARAMETER MEASUREMENT INFORMATION 2×Vcc **TEST S**1 tPLH/tPHL Open 500 Ω Open From Output tpl.z/tpzl 2 × Vcc **♀GND Under Test** tPHZ/tPZH GND CL = 50 pF 500 Ω (see Note A) LOAD CIRCUIT Output 3 V Control (low-level enabling) tpl.Z Output Input ~Vcc 1.5 V 1.5 V Waveform 1 (see Note B) S1 at 2 × VCC VOL (see Note C) tpHZ-Output Vон ٧он

NOTES: A. CL includes probe and jig capacitance.

Output

B. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> = 3 ns, t<sub>f</sub> = 3 ns.

50% VCC

VOL

Waveform 2

(see Note C)

S1 at GND

80% VCC

~0 V

50% V<sub>C</sub>C

**VOLTAGE WAVEFORMS**

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

50% VCC

**VOLTAGE WAVEFORMS**

Figure 1. Load Circuit and Voltage Waveforms