# 74ABT823 9-Bit D-Type Flip-Flop with TRI-STATE® Outputs

#### **General Description**

The 'ABT823 is a 9-bit buffered register. It features Clock Enable and Clear which are ideal for parity bus interfacing in high performance microprogramming systems.

#### **Features**

- **TRI-STATE outputs**

- Clock Enable and Clear

- Guaranteed latch up protection

- Non-destructive hot insertion capability

- High impedance glitch free bus loading during entire power up and power down cycle

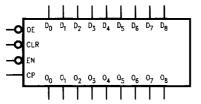

### **Logic Symbols**

TL/F/12108~1

## **Connection Diagram**

TL/F/12108-2

5

#### **Functional Description**

The 'ABT823 device consists of nine D-type edge-triggered flip-flops. It has TRI-STATE true outputs and is organized in broadside pinning. The buffered Clock (CP) and buffered Output Enable ( $\overline{OE}$ ) are common to all flip-flops. The flip-flops will store the state of their individual D inputs that meet the setup and hold times requirements on the LOW-to-HIGH CP transition. With the  $\overline{OE}$  LOW the contents of the flip-flops are available at the outputs. When the  $\overline{OE}$  is HIGH, the outputs go to the high impedance state. Operation of the  $\overline{OE}$  input does not affect the state of the flip-flops. In addi-

tion to the Clock and Output Enable pins, the 'ABT823 has Clear (CLR) and Clock Enable (EN) pins.

When the  $\overline{\text{CLR}}$  is LOW and the  $\overline{\text{OE}}$  is LOW, the outputs are LOW. When  $\overline{\text{CLR}}$  is HIGH, data can be entered into the flipflops. When  $\overline{\text{EN}}$  is LOW, data on the inputs is transferred to the outputs on the LOW to HIGH clock transition. When the  $\overline{\text{EN}}$  is HIGH, the outputs do not change state regardless of the data or clock inputs transitions. This device is ideal for parity bus interfacing in high performance systems.

**Function Table**

| Inputs |     |    |               |   | Internal | Output | Function          |

|--------|-----|----|---------------|---|----------|--------|-------------------|

| ŌĒ     | CLR | ĒÑ | СР            | D | ā        | 0      | Tanodon           |

| Н      |     | L  | Н             | Х | NC       | Z      | Hold              |

| н      | н   | L  | L             | X | NC       | z      | Hold              |

| н      | Н   | Н  | X             | Х | NC       | Z      | Hold              |

| L      | Н   | H  | Х             | X | NC       | NC     | Hold              |

| Н      | L   | Х  | Х             | Χ | н        | Z      | Clear             |

| L      | L   | X  | Х             | X | н        | L      | Clear             |

| Н      | Н   | L  | $\mathcal{L}$ | Н | н        | z      | Load              |

| Н      | H   | L  | $\mathcal{L}$ | Н | L        | z      | Load              |

| L      | Н   | L  | $\mathcal{L}$ | L | н        | L      | Data Available    |

| L      | H   | L  | $\mathcal{L}$ | Н | L        | Н      | Data Available    |

| L      | Н   | L  | Н             | X | NC       | NC     | No Change in Data |

| L      | Н   | Ł  | L             | X | NC       | NC     | No Change in Data |

L = LOW Voltage Level

H = HIGH Voltage Level

X = immaterial

Z - High Impedance

= LOW-to-HIGH Transition

NC = No Change

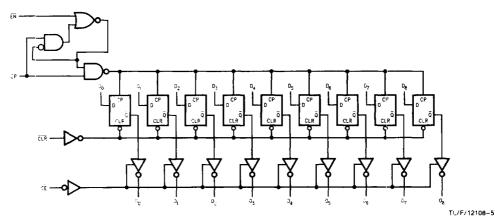

# **Logic Diagram**

Please no e that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.