TI0249-D3572, JUNE 1990

- Packaged in Shrink Small-Outline 300-mil Packages (SSOP) and 380-mil Fine-Pitch Ceramic Flat Packages Using 25-mil Center-to-Center Pin Spacings

- Inputs are TTL- or CMOS-Voltage Compatible

- 3-State Outputs Drive Bus Lines Directly

- Flow-Through Architecture Optimizes PCB Layout

- Distributed V<sub>CC</sub> and GND Pin Configuration Minimizes High-Speed Switching Noise

- EPIC™ (Enhanced-Performance Implanted CMOS) 1-µm Process

- 500-mA Typical Latch-Up Immunity at 125°C

## description

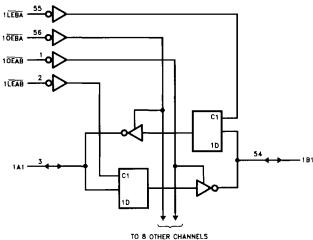

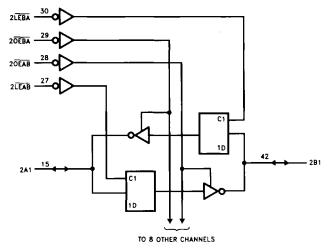

The 'AC16473 and 'ACT16473 are inverting 18-bit latched bus transceivers composed of two 9-bit sections with separate control signals. For either 9-bit transceiver section, data flow in the A-to-B mode is controlled by output enable (1OEAB or 2OEAB) and latch enable (1LEAB or 2LEAB) inputs. When 1OEAB (or 2OEAB) is low, the corresponding B outputs are active (high or low logic levels). When 10EAB (or 20EAB) is high, the corresponding B outputs are in the high-impedance state. The latches retain their prior states when 1LEAB (or 2LEAB) is high and reflect the states of the corresponding A inputs when 1LEAB (or 2LEAB) is low.

## 54AC16473, 54ACT16473 ... WD PACKAGE 74AC16473, 74ACT16473 ... DL PACKAGE (TOP VIEW) 10FAR DI VISADIOFRA

| 10EAB [           | 1           | <b>₩</b> 56 | ∐10EBA            |

|-------------------|-------------|-------------|-------------------|

| 1 LEAB            | 2           | 55          | 1 LEBA            |

| 1A1               | 3           | 54          | ]1B1              |

| GND [             | ]₄          | 53          | GND               |

| 1A2 [             | ]5          | 52          | ] 1B2             |

| 1A3 [             | 6           | 51          | ] 1B3             |

| V <sub>CC</sub> [ | 17          | 50          | □ V <sub>CC</sub> |

| 1A4               | ]8          | 49          | ] 1B4             |

| 1A5 [             | ]9          | 48          | ] 1 <b>B</b> 5    |

| 1A6 [             | 10          | 47          | ] 1B6             |

| GND [             | <b>]</b> 11 | 46          | GND               |

| 1A7 [             | 12          | 45          | ] 187             |

| 1A8 [             | 13          | 44          | ]1B8              |

| 1A9 [             | 14          | 43          | ] 1 B9            |

| 2A1[              | 15          | 42          | □ 2B1             |

| 2A2 [             | 16          | 41          | ] 2B2             |

| 2A3 [             | ]17         | 40          | _ 2B3             |

| GND [             | 18          | 39          | GND               |

| 2A4 [             | ]19         | 38          | <b>284</b>        |

| 2A5 [             | 20          | 37          | 285               |

| 2 <b>A</b> 6 [    | 21          | 36          | 286               |

| V <sub>cc</sub> [ | 22          | 35          | □v <sub>cc</sub>  |

| 2A7 [             | 23          | 34          | 287               |

| 2A8 [             | 24          | 33          | ] 2B8             |

| GND [             | 25          | 32          | GND               |

| 2A9 [             | ]26         | 31          | ☐ 2B9             |

| 2LEAB [           | 27          | 30          | 2LEBA             |

| 20EAB             | ]28         | 29          | 20EBA             |

## **FUNCTION TABLE, EACH SECTION<sup>†</sup>**

| INP  | UTS  |                 | B OUTPUTS                  |  |

|------|------|-----------------|----------------------------|--|

| LEAB | OEAB | LATCH DATA      |                            |  |

| L    | L    | Current A Data  | Inverse of Current A Data  |  |

| H    | L    | Previous A Data | Inverse of Previous A Data |  |

| L    | Н    | Current A Data  | Z                          |  |

| H    | H    | Previous A Data | Z                          |  |

<sup>&</sup>lt;sup>†</sup> A-to-B data flow is shown. B-to-A data flow is controlled analogously by OEBA and LEBA.

EPIC and Widebus are trademarks of Texas Instruments Incorporated.

PRODUCT PREVIEW documents contain information on products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas instruments reserves the right to change or discontinue these products without notice.

PRODUCT PREVIE

TI0249-D3572, JUNE 1990

Data flow from B to A is similar, but uses 10EBA and/or 20EBA and 1LEBA and/or 2LEBA.

The 74AC16473 and 74ACT16473 are packaged in TI's shrink small-outline package (SSOP) with 25-mil center-to-center pin spacings. This package provides twice the I/O pin count and functionality of a standard small-outline package in the same printed-circuit-board area.

The 'AC16473 has CMOS-compatible input thresholds. The 'ACT16473 has TTL-compatible input thresholds.

The 54AC16473 and 54ACT16473 are characterized over the full military temperature range of -55°C to 125°C. The 74AC16473 and 74ACT16473 are characterized for operation from -40°C to 85°C.

## logic diagram (positive logic)

PRODUCT PREVIEW