# Quad D-Type Flip-Flop with Complementary Outputs/Common Direct Clear

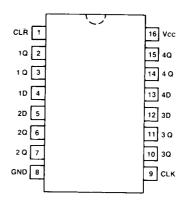

The LS175 is a bipolar, NPN, sealed-junction, silicon integrated circuit. It is manufactured in low-power Schottky technology and is available in a wire-bonded, 16-pin plastic DIP or surface mount package.

#### Truth Table (Each Flip-Flop)

| Inputs |       |   | Outputs |                           |  |

|--------|-------|---|---------|---------------------------|--|

| Clear  | Clock | D | Q       | Q                         |  |

| L      | Х     | Х | L       | Н                         |  |

| н      | 1     | Н | Н       | L                         |  |

| Н      | 1     | L | L       | Н                         |  |

| H      | L     | Х | Qo      | $\overline{\mathbf{Q}}_0$ |  |

H = High level (steady state)

L = Low level (steady state)

X = Irrelevant

1 = Transition from low to high level

Q0= The level of Q before the indicated steady state input conditions were established

$\overline{\mathbb{Q}}_0$  = Complement of  $\mathbb{Q}_0$  or level of  $\overline{\mathbb{Q}}_0$  before the indicated steady-state input conditions were established

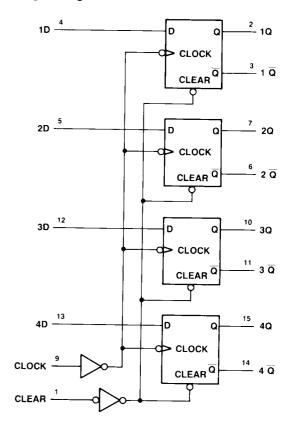

## Logic Diagram

#### **Electrical Characteristics**

$VCC = 5.0 \pm 0.5 \text{ V}, TA = -55 \text{ to } +125^{\circ}\text{C (WA-LS)}$

$VCC = 5.0 \pm 0.25 \text{ V}, TA = 0 \text{ to } 70^{\circ}\text{C (WP90350L1)}$

$VCC = 5.0 \pm 0.5 \text{ V}, \text{ TA} = -40 \text{ to } +85^{\circ}\text{C} \text{ (WA-LSD, WP91399L2)}$

|                                                                                                                                              |                   | WA-LS         |                    | WP, WA-LSD    |                     |                |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|--------------------|---------------|---------------------|----------------|

| Parameter                                                                                                                                    | Symbol            | Min           | Max                | Min           | Max                 | Units          |

| Output Voltage, VCC = 4.5 V (WA-LS), 4.75 V (WP, WA-LSD) Low, IOL = 4.0 mA IOL = 8.0 mA High, IOH = -0.4 mA                                  | Vol<br>Vol<br>Voh | _<br>_<br>2.5 | 0.4<br>0.5<br>—    | _<br>_<br>2.7 | 0.4<br>0.5          | < < <          |

| Input Voltage, VCC = 4.5 V (WA-LS), 4.75 V (WP, WA-LSD) Low High Clamp, IIN = -18.0 mA                                                       | VIL<br>VIH<br>VIK | _<br>2.0<br>_ | 0.7<br>7.5<br>–1.5 | <br>2.0<br>   | 0.8*<br>5.5<br>–1.5 | V<br>V<br>V    |

| Input Current, VCC = 5.5 V (WA-LS), 5.25 V (WP, WA-LSD) Low, VIL = 0.4 V High, VIH = 2.7 V  @ VI max, VI = 7.0 V (WA-LS), 5.5 V (WP, WA-LSD) | lıL<br>lıH<br>lı  | 1 1 1         | 0.4<br>20.0<br>0.1 | _<br>_<br>_   | -0.4<br>20.0<br>0.1 | mΑ<br>μΑ<br>mA |

| Output Current, Vcc = 5.5 V (WA-LS), 5.25 V (WP, WA-LSD) Short-Circuit                                                                       | los               | -20.0         | -100.0             | -20.0         | -100.0              | mA             |

| Supply Current, Vcc = 5.5 V (Outputs Open, Data and Clear High, Clock Momentary Ground; then High)                                           | Icc               | _             | 18.0               |               | 18.0                | mA             |

<sup>\*</sup> WA-LSD, WP91399L2: VIL = 0.7 V

### **Timing Characteristics**

VCC = 5.0 V, TA = 25°C, CL = 15 pF

|                           |              | WA-  | -LS  | WP, W | A-LSD |       |

|---------------------------|--------------|------|------|-------|-------|-------|

| Parameter                 | Symbol       | Min  | Max  | Min   | Max   | Units |

| Propagation Delay         |              |      |      |       |       |       |

| Clear-to-Output           | •            |      |      |       |       |       |

| Low-to-High               | <b>t</b> PLH | _    | 25.0 |       | 30.0  | ns    |

| High-to-Low               | <b>t</b> PHL | _    | 28.0 | _     | 30.0  | ns    |

| Clock-to-Output           |              |      |      |       |       |       |

| Low-to-High               | telh         | _    | 20.0 | _     | 25.0  | ns    |

| High-to-Low               | tphL         | _    | 22.0 | _     | 25.0  | ns    |

| Operating Conditions      |              |      |      | -     |       |       |

| Width of Clock Pulse      | tw           | 20.0 |      | 20.0  | _     | ns    |

| Setup Time                |              |      |      |       |       |       |

| Data, Low                 | tosL         | 5.0  | _    | 20.0  |       | ns    |

| High                      | tosh         | 0    | _    | 20.0  | _     | ns    |

| Clear Inactive State, Low | tosl         | 25.0 | _    | 25.0  | _     | ns    |

| High                      | tosh         | 25.0 | _    | 25.0  | _     | ns    |

| Data Hold Time, Low       | tonu         | 10.0 | _    | 5.0   | _     | ns    |

| High                      | tonn         | 10.0 | _    | 5.0   |       | ns    |

| Maximum Clock Frequency   | fmax         | 30.0 | _    | 30.0  |       | MHz   |

# **Maximum Ratings**

| Power supply voltage (VCC)                                           |                                              |

|----------------------------------------------------------------------|----------------------------------------------|

| Operating temperature (Ta)                                           | WA-LS: -55 to +125°C                         |

|                                                                      | WP90350L1: 0 to 70°C                         |

|                                                                      | WA-LSD, WP91399L2: -40 to +85°C              |

| Storage temperature (Tstg)                                           |                                              |

| Maximum ratings are defined as the limiting conditions that the user | can apply to the device under all variations |

of circuit and environmental conditions. If any rating is exceeded, permanent damage to the device may result.

Bonding or soldering of the external leads of this device can be performed safely at temperatures up to 300°C.

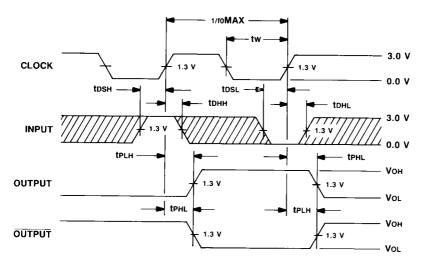

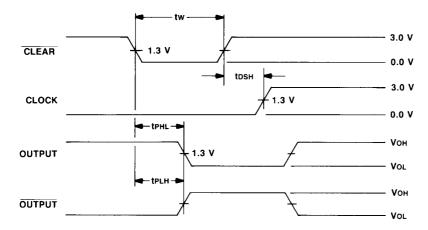

## **Timing Diagrams**

THE SHADED AREAS INDICATE WHEN THE INPUT IS PERMITTED TO CHANGE FOR PREDICTABLE OUTPUT PERFORMANCE

Figure 1. Clear to Output Delay, Clear Pulse Width, and Clearing Time

Figure 2. Clock to Output Delays, Clock Pulse Width, Frequency, Set-Up and Hold Times Data to Clock