#### **Features**

- 16 non-inverting buffers with three-state outputs

- Guaranteed simultaneously switching noise level and dynamic threshold performance

- Separate control logic for each byte and nibble

- 0.6μm Commercial RadHard™ CMOS

- Total dose: 100K rad(Si)

- Single Event Latchup immune

- High speed, low power consumption

- Output source/sink 24mA

- Standard Microcircuit Drawing 5962-06243

- QML compliant part

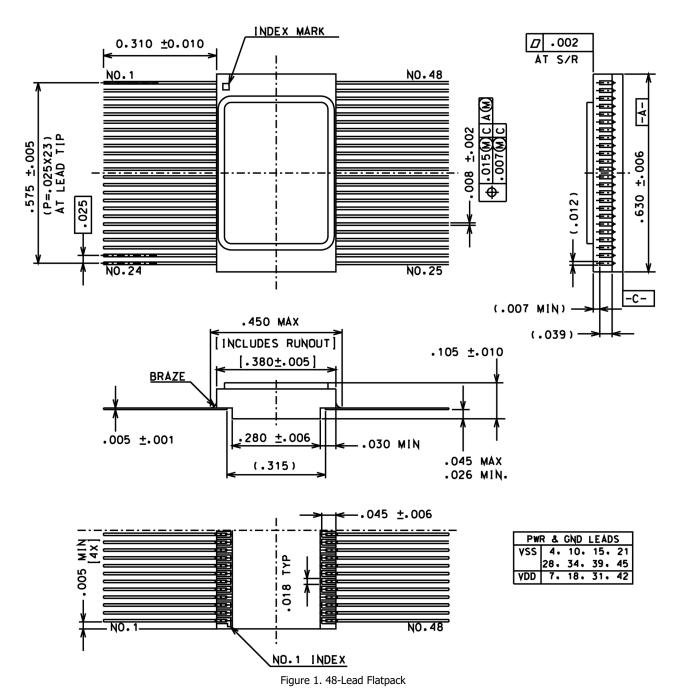

- Package:

- 48-lead flatpack, 25 mil pitch (.390 x .640)

### **Description**

The 16-bit wide UT54ACTQ16244 buffer/line driver is built using CAES Commercial RadHard<sup>™</sup> epitaxial CMOS technology and is ideal for space applications. This high speed, low power UT54ACTQ16244 buffer/line driver is designed to improve the performance and density of three-state memory address drivers, clock drivers, and busoriented receivers and transmitters. The UT54ACTQ16244 can be used as four 4-bit (nibble) buffers, two 8-bit (byte) buffers, or one 16-bit buffer. The device provides true outputs and symmetrical  $\overline{\text{OE}}$  (active-low) outputenable inputs. The device is nibble controlled with each nibble functioning identically, but independent of each other. The control pins can be shorted together to obtain full 16-bit operation.

### **Pin Description**

| Pin Names       | Description                      |

|-----------------|----------------------------------|

| <del>OE</del> n | Output Enable Input (Active Low) |

| I0-I15          | Inputs                           |

| 00-015          | Outputs                          |

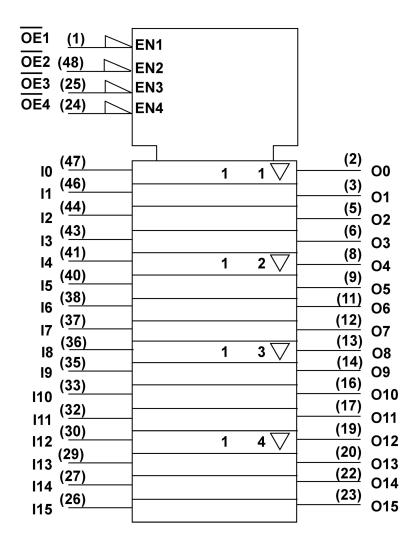

### **Logic Symbol**

### **Function Table**

| Enable  OE1, OE2,  OE3, OE4 | Inputs<br>I0-I3, I4-I7,<br>I8-I11, I12-I15 | Outputs<br>00-03, 04-07,<br>08-011, 012-015 |

|-----------------------------|--------------------------------------------|---------------------------------------------|

| L                           | L                                          | L                                           |

| L                           | Н                                          | Н                                           |

| Н                           | X                                          | Z                                           |

### **Pinouts**

| OE1             | 1  | 48        |   | OE2        |

|-----------------|----|-----------|---|------------|

| 00              | 2  | 47        |   | 10         |

| 01              | 3  | 46        |   | <b>I1</b>  |

| $V_{SS}$        | 4  | 45        |   | $v_{ss}$   |

| 02              | 5  | 44        |   | 12         |

| О3              | 6  | 43        |   | 13         |

| $V_{DD}$        | 7  | 42        |   | $V_{DD}$   |

| 04              | 8  | 41        |   | 14         |

| <b>O5</b>       | 9  | 40        |   | 15         |

| $V_{SS}$        | 10 | 39        |   | $V_{SS}$   |

| <b>O6</b>       | 11 | 38        |   | 16         |

| 07              | 12 | 37        |   | <b>17</b>  |

| 08              | 13 | 36        |   | 18         |

| 09              | 14 | 35        |   | 19         |

| $V_{SS}$        | 15 | 34        |   | $V_{SS}$   |

| 010             | 16 | 33        |   | <b>I10</b> |

| 011             | 17 | 32        |   | <b>I11</b> |

| $V_{DD}$        | 18 | 31        |   | $V_{DD}$   |

| 012             | 19 | 30        |   | <b>I12</b> |

| 013             | 20 | 29        |   | <b>I13</b> |

| V <sub>SS</sub> | 21 | 28        |   | $V_{SS}$   |

| 014             | 22 | <b>27</b> |   | <b>I14</b> |

| 015             | 23 | 26        |   | <b>I15</b> |

| OE4             | 24 | 25        |   | OE3        |

|                 |    |           | I |            |

48-Lead Flatpack Top View

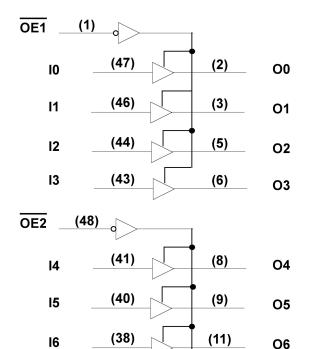

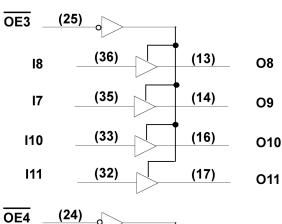

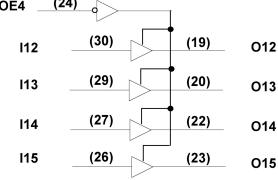

### **Logic Diagram**

### Radiation Hardness Specifications <sup>1</sup>

(37)

| Parameter                    | Limit            | Units                   |

|------------------------------|------------------|-------------------------|

| Total Dose                   | 1.0E5            | rad(Si)                 |

| SEL Immune                   | >108             | MeV-cm <sup>2</sup> /mg |

| SEU Onset Let                | N/A <sup>3</sup> | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence <sup>2</sup> | 1.0E14           | n/cm²                   |

#### Notes:

17

1) Logic will not latchup during radiation exposure within the limits defined in the table.

07

- 2) Not tested, inherent of CMOS technology.

- 3) This device contains no memory storage elements which can be upset.

(12)

RadHard CMOS 16-bit Buffer/Line Driver, TTL Inputs, and Three-State Outputs

## UT54ACTQ16244

### **Absolute Maximum Ratings <sup>1</sup>**

| Symbol                | Parameter                           | Limit (mil only)         | Units |

|-----------------------|-------------------------------------|--------------------------|-------|

| $V_{\rm I/O}$         | Voltage any pin during operation    | 3 to V <sub>DD</sub> +.3 | V     |

| $V_{DD}$              | Supply voltage                      | -0.3 to 6.0              | V     |

| T <sub>STG</sub>      | Storage Temperature range           | -65 to +150              | °C    |

| T <sub>J</sub>        | Maximum junction temperature        | +175                     | °C    |

| $\Theta_{	exttt{JC}}$ | Thermal resistance junction to case | 20                       | °C/W  |

| $I_{\rm I}$           | DC input current                    | ±10                      | mA    |

| P <sub>D</sub>        | Maximum power dissipation           | 310                      | mW    |

#### Note:

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating

only, functional operation of the device at these or any other condition beyond limits indicated in the operational sections is

not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and

performance.

### **Recommended Operating Conditions**

| Symbol             | Parameter                                                                                                                                                                                    | Limit                | Units |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|

| $V_{DD}$           | Supply voltage                                                                                                                                                                               | 4.5 to 5.5           | V     |

| $V_{\mathrm{IN}}$  | Input voltage any pin                                                                                                                                                                        | 0 to V <sub>DD</sub> | V     |

| T <sub>C</sub>     | Temperature range                                                                                                                                                                            | -55 to + 125         | °C    |

| tinrise<br>tinfall | $\label{eq:maximize} \begin{array}{l} \text{Maximize input rise or fall time} \\ (V_{IN}  \text{transitioning between } V_{IL}  (\text{max})  \text{and } V_{IH}  (\text{min})) \end{array}$ | 20                   | ns    |

### **DC Electrical Characteristics <sup>1</sup>**

$(-55^{\circ}C < T_{C} < +125^{\circ}C)$

| Symbol             | Parameter                                       | Condition                                                                    |                        | MIN                    | MAX  | Unit   |

|--------------------|-------------------------------------------------|------------------------------------------------------------------------------|------------------------|------------------------|------|--------|

| $V_{\mathrm{IL}}$  | Low level input voltage <sup>2</sup>            | V <sub>DD</sub> from 4.5 to 5.5V                                             |                        |                        | 0.8  | V      |

| $V_{\mathrm{IH}}$  | High level input voltage <sup>2</sup>           | V <sub>DD</sub> from 4.5 to 5.5V                                             |                        | 2.0                    |      | V      |

| ${ m I_{IN}}$      | Input leakage current <sup>3</sup>              | $V_{DD}$ from 4.5V to 5.5V $V_{IN} = V_{DD}$ or $V_{SS}$                     | 1                      | -1                     | 1    | μА     |

| $I_{OZ}$           | Three-state output leakage current <sup>3</sup> | $V_{DD}$ from 4.5V to 5.5V $V_{IN}$ = $V_{DD}$ or $V_{SS}$                   | 1                      | -10                    | 10   | μА     |

| I <sub>OS</sub>    | Short-circuit output current 4, 5               | $V_O = V_{DD}$ or $V_{SS}$<br>$V_{DD}$ from 4.5V to 5.5V                     | 1                      | -600                   | 600  | mA     |

|                    |                                                 | I <sub>OL</sub> =24mA                                                        | -55°C, 25°C            |                        | 0.36 |        |

| V                  | Low-level output voltage 3, 6                   | I <sub>OL</sub> =24mA                                                        | +125°C                 |                        | 0.5  | V      |

| $V_{OL1}$          | Low-level output voltage 973                    | $I_{OL}$ =100 $\mu$ A<br>$V_{DD}$ = 4.5V to 5.5V<br>$V_{IN}$ = 0.8V to 2.0V  | -55°C, 25°C,<br>+125°C |                        | 0.2  | V      |

|                    |                                                 | I <sub>OL</sub> = 50mA                                                       | -55°C, 25°C            |                        | 0.8  |        |

| $V_{OL2}$          | Low-level output voltage <sup>3, 6, 7</sup>     | $V_{IN}$ = 2.0V or 0.8V $V_{DD}$ = 5.5V $V_{IN}$ = 0.8V to 2.0V              | +125°C                 |                        | 1.0  | V      |

|                    |                                                 | I <sub>OH</sub> =-24mA                                                       | -55°C, 25°C            | V <sub>DD</sub> - 0.64 |      |        |

| V                  | Illah lawal autout walta aa 3.6                 | I <sub>OH</sub> =-24mA                                                       | +125°C                 | V <sub>DD</sub> - 0.8  |      | .,     |

| $V_{OH1}$          | High-level output voltage <sup>3, 6</sup>       | $I_{OH}$ =-100 $\mu$ A<br>$V_{DD}$ = 4.5V to 5.5V<br>$V_{IN}$ = 0.8V to 2.0V | -55°C, 25°C,<br>+125°C | V <sub>DD</sub> - 0.2  |      | V      |

|                    |                                                 | I <sub>OH</sub> =-50mA                                                       | -55°C, 25°C            | V <sub>DD</sub> - 1.1  |      |        |

| $V_{\mathrm{OH2}}$ | High-level output voltage <sup>3, 6, 7</sup>    | $V_{IN}$ =2.0V or 0.8V $V_{DD}$ =5.5V $V_{IN}$ =0.8V to 2.0V                 | +125℃                  | V <sub>DD</sub> - 1.3  |      | V      |

| V <sub>IC</sub> +  | Positive input clamp voltage                    | For input under test, $I_{\text{IN}}$ = 18mA $V_{\text{DD}}$ = 0.0V          |                        | 0.4                    | 1.5  | V      |

| V <sub>IC</sub> -  | Negative input clamp voltage                    | For input under test, $I_{IN}$ =-18mA $V_{DD}$ = open                        |                        | -1.5                   | -0.4 | V      |

| P <sub>total</sub> | Power dissipation <sup>8, 9, 10</sup>           | C <sub>L</sub> = 20pF<br>V <sub>DD</sub> from 4.5V to 5.5V                   |                        |                        | 1.0  | mW/MHz |

#### DC Electrical Characteristics 1

$(-55^{\circ}C < T_C < +125^{\circ}C)$

| Symbol                                | Parameter                                                                                 | Condition                                                                                                                                                                 | MIN | MAX                                                  | Unit     |

|---------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------|----------|

| ${ m I}_{ m DDQ}$                     | Standby Supply Current V <sub>DD</sub> Pre-Rad 25°C Pre-Rad -55°C to +125°C Post-Rad 25°C | $\begin{aligned} &V_{IN} = V_{DD} \text{ or } V_{SS} \\ &V_{DD} = 5.5V \\ &\overline{OE}n = V_{DD} \\ &\overline{OE}n = V_{DD} \\ &\overline{OE}n = V_{DD} \end{aligned}$ |     | 10<br>160<br>160                                     | μА       |

| $\Delta I_{DDQ}$                      | Quiescent Supply Current Delta,<br>TTL input level                                        | For input under test $V_{IN} = V_{DD} - 2.1V$ For other inputs $V_{IN} = V_{DD} \text{ or } V_{SS}$ $V_{DD} = 5.5V$                                                       |     | 1.6                                                  | mA       |

| C <sub>IN</sub>                       | Input capacitance 11                                                                      | f = 1MHz @ 0V<br>V <sub>DD</sub> from 4.5V to 5.5V                                                                                                                        |     | 15                                                   | pF       |

| Соит                                  | Output capacitance 11                                                                     | f = 1MHz @ 0V<br>V <sub>DD</sub> from 4.5V to 5.5V                                                                                                                        |     | 15                                                   | pF       |

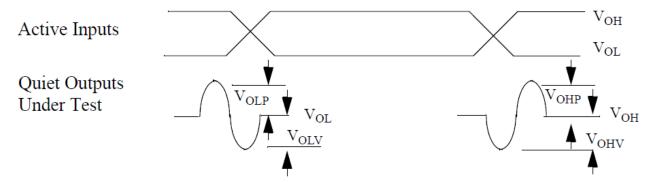

| $oldsymbol{V}_OLP \ oldsymbol{V}_OLV$ | Low level V <sub>SS</sub> bounce noise <sup>12</sup>                                      | $V_{IH} = 3.0V, V_{IL} = 0.0V,$<br>$T_A = +25^{\circ}C, V_{DD} = 5.0V$                                                                                                    |     | 1000<br>-1000                                        | mV<br>mV |

| V <sub>OHP</sub><br>V <sub>OHV</sub>  | High level V <sub>DD</sub> bounce noise <sup>12</sup>                                     | See figure "Quiet Output Under<br>Test"                                                                                                                                   |     | V <sub>OH</sub><br>+1000<br>V <sub>OH</sub><br>-1300 | mV<br>mV |

#### **Notes:**

- All specifications valid for radiation dose ≤ 1E5 rad(Si) per MIL-STD-883, Method 1019.

- 2) Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions:  $V_{IH}=V_{IH}(min) + 20\%$ , 0%;  $V_{IL}=V_{IL}(max) + 0\%$ , 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to  $V_{IH}(min)$  and  $V_{IL}(max)$ .

- 3) Guaranteed; tested on a sample of pins per device.

- 4) Not more than one output may be shorted at a time for maximum duration of one second.

- 5) Supplied as a design limit, but not guaranteed or tested.

- 6) Per MIL-PRF-38535, for current density ≤ 5.0E5 amps/cm², the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765 pF-MHz.

- 7) Transmission driving tests are performed at  $V_{DD} = 5.5V$ , only one output loaded at a time with a duration not to exceed 2ms. The test is guaranteed, if not tested, for  $V_{IN}=V_{IH}$  minimum or  $V_{IL}$  maximum.

- 8) Guaranteed by characterization.

- 9) Power does not include power contribution of any CMOS output sink current.

- 10) Power dissipation specified per switching output.

- 11) Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and V<sub>SS</sub> at frequency of 1MHz and a signal amplitude of 50mV rms maximum.

- 12) This test is for qualification only.  $V_{SS}$  and  $V_{DD}$  bounce tests are performed on a non-switching (quiescent) output and are used to measure the magnitude of induced noise caused by other simultaneously switching outputs. The test is performed on a low noise bench test fixture.

### **AC Electrical Characteristics <sup>1</sup>**

$(V_{DD} = 5V \pm 10\%; -55^{\circ}C < T_{C} < +125^{\circ}C)$

| Symbol                          | Parameter                         | MIN | MAX | Unit |

|---------------------------------|-----------------------------------|-----|-----|------|

| t <sub>PLH</sub>                | Propagation delay In to On        | 2   | 8.0 | ns   |

| t <sub>PHL</sub>                | Propagation delay In to On        | 2   | 8.0 | ns   |

| t <sub>PZL</sub>                | Output hold time OEn to On        | 2   | 8.0 | ns   |

| t <sub>PZH</sub>                | Output enable time OEn to On      | 2   | 8.0 | ns   |

| t <sub>PLZ</sub>                | Output enable time OEn to On      | 2   | 9.5 | ns   |

| t <sub>PHZ</sub>                | Output disable time OEn to On     | 2   | 9.5 | ns   |

| t <sub>SKEW</sub> <sup>2</sup>  | Output-to-output skew             | -   | 1.0 | ns   |

| t <sub>DSKEW</sub> <sup>3</sup> | Differential skew between outputs |     | 1.6 | ns   |

| t <sub>SKEWPP</sub> 2, 4        | Part-to-Part output skew          |     | 500 | ps   |

#### Notes:

- 1) All specifications valid for radiation dose  $\leq$  1E5 rad(Si) per MIL-STD-883, Method 1019.

- 2) Output skew is defined as a comparison of any two output transitions high-to-low vs. high-to-low and low-to-high vs low-to-high.

- 3) Differential skew is defined as a comparison of any two output transitions high-to-low vs. low-to-high and low-to-high vs high-to low.

- 4) Guaranteed by characterization, but not tested.

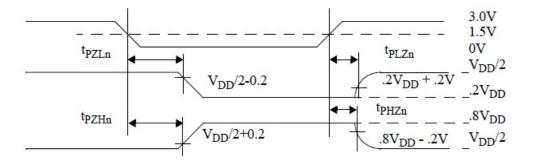

### **Propagation Delay**

Input  $\begin{array}{c} 3.0V \\ 1.5V \\ 0V \\ \end{array}$  Output  $\begin{array}{c} V_{OH} \\ V_{DD}/2 \\ V_{OL} \\ \end{array}$

#### **Enable Disable Times**

Control Input

5V Output Normally Low 5V Output Normally High

RadHard CMOS 16-bit Buffer/Line Driver, TTL Inputs, and Three-State Outputs

## UT54ACTQ16244

### **Bounce Noise**

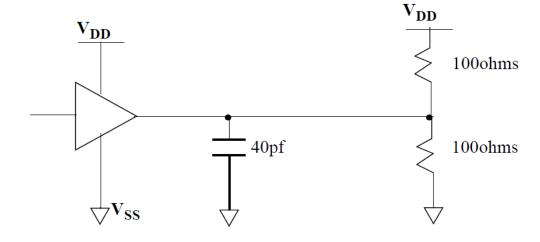

### Test Load or Equivalent <sup>1</sup>

#### Note:

1) Equivalent test circuit means that DUT performance will be correlated and remain guaranteed to the applicable test circuit, above, whenever a test platform change necessitates a deviation from the applicable test circuit.

### **Package**

Notes:

- 1) Seal ring is connected to  $V_{\text{SS}}$ .

- 2) Units are in inches.

- 3) All exposed metalized areas must be gold plated 100 to 225 microinches thick. Dyer electroplated nickel undercoating 100 to 350 microinches per MIL-PRF-38535.

### **Ordering Information**

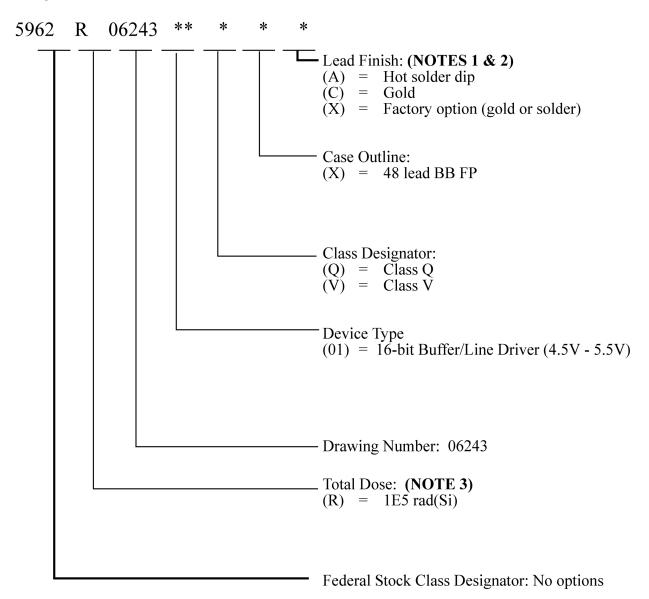

UT54ACTQ16244: SMD

#### Notes:

- 1) Lead finish (A,C, or X) must be specified.

- 2) If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3) Total dose radiation must be specified when ordering. QML Q not available without radiation hardening Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening.

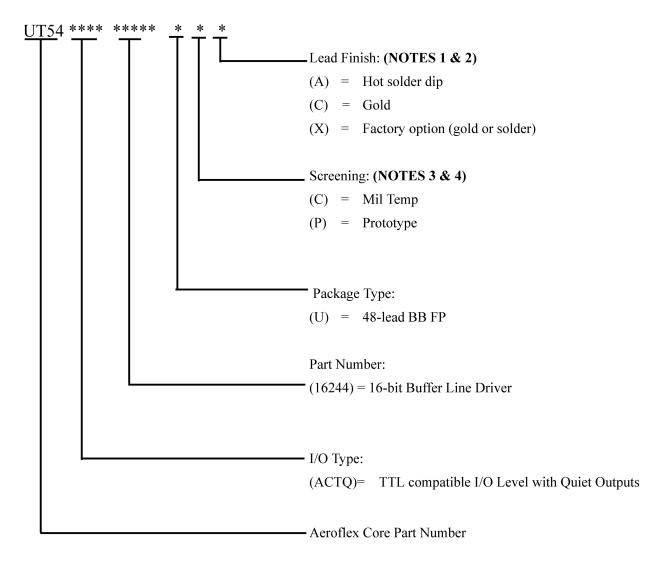

#### UT54ACTQ16244

#### Notes:

- 1) Lead finish (A, C, or X) must be specified.

- 2) If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3) Prototype flow per CAES Manufacturing Flows Document. Tested at 25°C only. Lead finish is Gold "C" only. Radiation neither tested nor guaranteed.

- 4) Military Temperature Range flow per CAES Manufacturing Flows Document. Devices are tested at -55°C, room temp, and 125°C. Radiation neither tested nor guaranteed.

RadHard CMOS 16-bit Buffer/Line Driver, TTL Inputs, and Three-State Outputs

## UT54ACTQ16244

#### **Datasheet Definitions**

|                       | DEFINITION                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the datasheet <b>is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                             |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties