#### **Features**

- Offset voltage 3 mV maximum over temperature

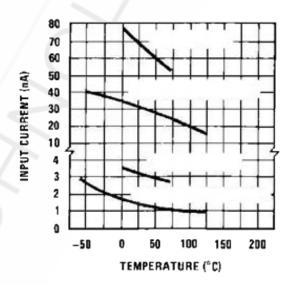

- Input current 100 nA maximum over temperature

- Offset current 20 nA maximum over temperature

- Guaranteed drift characteristics

- Offsets guaranteed over entire common mode and supply voltage ranges

- Slew rate of 10V/us as a summing amplifier

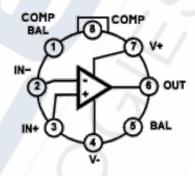

#### **Pinout**

8-lead metal can Top View

Package pinout

### **Operational Amplfiers**

The FT101ASH5U is a general purpose operational amplifier which features improved performance over industry standards such as the LM709. Advanced processing techniques make possible an order of magnitude reduction in input currents, and a redesign of the biasing circuitry reduces the temperature drift of input current. This amplifier offers many features which make its application nearly foolproof: overload protection on the input and output, no latch up when the common mode range is exceeded, and freedom from oscillations and compensation with a single 30pF capacitor. It has advantages over internally compensated amplifiers in that the frequency compensation can be tailored to the particular application. For example, in low frequency circuits it can be overcompensated for increased stability margin. Or the compensation can be optimised to give more than a factor of ten improvement in high frequency performance for most applications. In addition, the device provides better accuracy and lower noise in high impedance circuitry. The low input currents also make it particularly well suited for long interval integrators or timers, sample and hold circuits and low frequency waveform generators. Further, replacing circuits where matched transistor pairs buffer the inputs of conventional IC op amps, it can give lower offset voltage and a drift at a lower cost.

## **Absolute Maximum Ratings**

Supply Voltage ±22V

Differential Input Voltage ±30V

Input Voltage(Note 2) ±15V

Output Short Circuit Duration(Note 3) Continuous

Total Power 750mW

Storage Temperature Range -65°C <Ta<+150°C

ESD Tolerance(Note 4) 3500V

Notes:

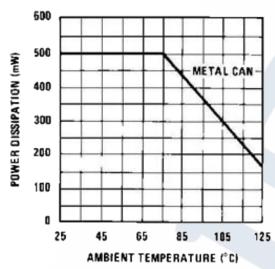

- 2. The maximum power dissipation must be derated at elevated temperatures and is dictated by Tjmax (maximum junction temperature), ThetaJA (package junction to ambient thermal resistance), and TA (ambient temperature). The maximum allowable power dissipation at any temperature is Pdmax = (Tjmax TA)/ThetaJA or the number given in the Absolute Maximum Ratings, whichever is lower.

- 3. For supply voltages less than +15V, the absolute maximum input voltage is equal to the supply voltage.

- 4. Human body model, 100 pF discharged through 1.5k Ohms.

#### **Thermal Information**

Thermal Resistance (typical)  $\theta_{JA} = 170 \text{ °C/W (note 1)}$

$\theta_{JC} = 85 \text{ °C/W (note 2)}$

**Maximum Junction Temperature**

150°C

300°C

Lead Temperature

(Soldering, 10 seconds)

Notes:

- 5.  $\theta_{JA}$  is measured with component on an evaluation PC board in free air

- 6. For  $\theta_{\text{JC}}$  "case temp" location is the center of metal can

## **Electrical Specifications**

$V_{SUPPLY} = \pm 15 \text{ V}$

| Parameter                           | Temp., °C  | FT101ASH5U/<br>FT201ASH5A |             |      | FT301ASH5J |      |     | Units  |

|-------------------------------------|------------|---------------------------|-------------|------|------------|------|-----|--------|

|                                     |            | Min                       | Тур         | Max  | Min        | Тур  | Max |        |

|                                     |            | Input (                   | Characteris | tics |            |      |     |        |

| Input Offset Voltage ,              | 25         | -2                        | 0.5         | 2    | -2         | 0.5  | 2   |        |

| •                                   | Tmax       | -3                        | -           | 3    | -3         | -    | 3   | mV     |

| Rs ≤ 50kΩ                           | Tmin       | -3                        | -           | 3    | -3         | -    | 3   |        |

| Offset Voltage Drift ,<br>Rs ≤ 50kΩ |            | -15                       | 10          | 15   | -15        | 10   | 15  | μV/°C  |

|                                     | 25         | -                         | 30          | 75   | -          | 30   | 75  |        |

| Input Bias Current                  | Tmax       | 1                         | 15          | 75   | -          | 20   | 75  | nA     |

|                                     | Tmin       | -                         | 45          | 100  | -          | 35   | 100 |        |

| Input Offset Current                | 25         | -10                       | -           | 10   | -10        | -    | 10  |        |

| Imput Offset Current                | Tmax       | -10                       | -           | 10   | -10        | -    | 10  | nA     |

|                                     | Tmin       | -20                       | -           | 20   | -20        | -    | 20  |        |

| Offset Current Drift                | 25 to Tmax | -0.1                      | 0.05        | 0.1  | -0.1       | 0.05 | 0.1 | nA/°C  |

| Onset Current Dilit                 | Tmin to 25 | -0.2                      | 0.07        | 0.2  | -0.2       | 0.07 | 0.2 | TIA, C |

| Parameter                                                            | Temp.,<br>°C |            | Г101ASH5<br>Г201ASH5 | -       | FT301ASH5J |     |      | Units |

|----------------------------------------------------------------------|--------------|------------|----------------------|---------|------------|-----|------|-------|

|                                                                      | L            | Min        | Тур                  | Max     | Min        | Тур | Max  |       |

| Maximum Common Mode                                                  | 25           | +11        | +13                  | -       | +11        | +13 | / -( |       |

| Voltage, $R_L$ = 2k $\Omega$                                         | Tmax         | +11        | +13                  | -       | +11        | +13 | 1    | V     |

| Voltage,N[-2K12                                                      | Tmin         | +11        | +13                  | 1       | +11        | +13 | /-/  | A     |

| Minimum Common Modo                                                  | 25           | -          | -13                  | -11     | 1          | -13 | -11  |       |

| Minimum Common Mode<br>Voltage                                       | Tmax         | -          | -13                  | -11     | -          | -13 | -11  | V     |

|                                                                      | Tmin         | -          | -13                  | -11     |            | -13 | -11  |       |

| Input Resistance                                                     | 25           | 1.5        | 4                    | -       | 1.5        | 4   | -    | kΩ    |

|                                                                      |              | Transfer c | haracteris           | tics    |            |     |      |       |

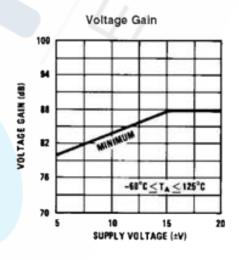

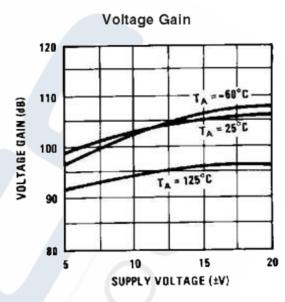

| Largo Signal Voltago Gain                                            | 25           | 80         | 160                  | -       | 80         | 160 | -    |       |

| Large Signal Voltage Gain V <sub>OUT</sub> =±10V,R <sub>L</sub> =2kΩ | Tmax         | 80         | 160                  | -       | 80         | 160 | 1    | kV/V  |

| V <sub>0UT</sub> -±10V,N <sub>L</sub> -2K\$2                         | Tmin         | 40         | 80                   | -       | 40         | 80  | 1    |       |

| Common Mada Rajastian                                                | 25           | 80         | 96                   | -       | 80         | 96  | 1    |       |

| Common Mode Rejection<br>Ratio , Rs ≤ 50kΩ                           | Tmax         | 80         | 85                   | -       | 80         | 85  | 1    | dB    |

| Natio, NS \( \) SUK\$2                                               | Tmin         | 80         | 85                   | -/      | 80         | 85  | 1    |       |

| Power Supply Characteristics                                         |              |            |                      | //      |            |     |      |       |

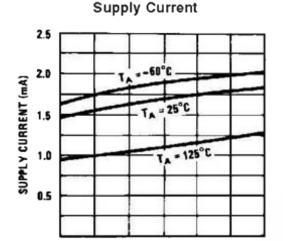

|                                                                      | 25           | -          | 1.5                  | 2.0     | -)         | 1.5 | 2.0  |       |

| Supply Current                                                       | Tmax         | -          | 1.2                  | 2.0     |            | 1.2 | 2.0  | mA    |

|                                                                      | Tmin         | -          | 2.0                  | 3.0     |            | 2.0 | 3.0  |       |

| Supply Voltage Rejection<br>Ratio, Rs ≤ 50kΩ                         | 25           | 80         | 96                   | <u></u> | 70         | 96  | -    | dB    |

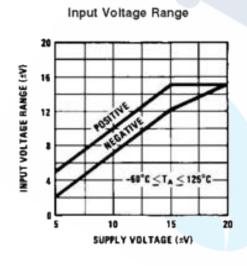

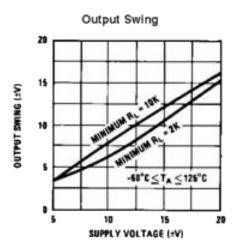

# **Typical Performance Characteristics**

### Maximum Power Dissipation

SUPPLY VOLTAGE (±V)

10

5

20

15

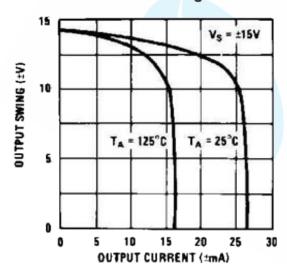

**Current Limiting**

Input Current,

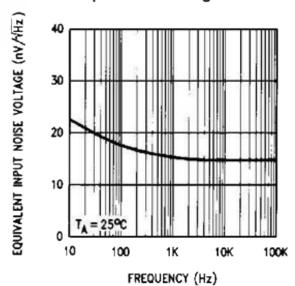

Input Noise Voltage

#### **Die Characteristics**

Die dimensions:

1.3x1.2± 0.1 mm,

51x47 ± 4 mils.

Wafer thickness 0.46± 0.02 mm,

18 ± 1 mils.

Metallisation:

type: Al, 1% Si, thickness:  $1.4 \pm 0.1 \mu m$

Glassivation:

type: Phosphosilicate glass (PSG) PSG thickness 1.2 ±0.2μm. Worst case current density:

$8.10^4 \text{ A/cm}^2$ .

Substrate potential(Powered Up):

Unbiased.

Transistor count:

24.

Process:

Bipolar epitaxial.

9AII

BAL

## **Metallisation Mask layout**

# BAL, COMP -IN +IN

COMP

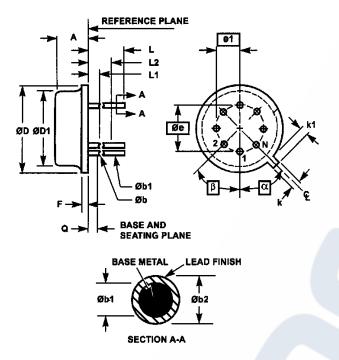

## Metal Can Package

#### Notes:

- (All leads) Øb applies between L1 and L2. Øb1 applies between L2 and 0.500 from the reference plane. Diameter is uncontrolled in L1 and beyond 0.500 from the reference plane.

- Measured from maximum diameter of the product.

- $\alpha$  is the basic spacing from the centerline of the tab to terminal 1 and  $\beta$  is the basic spacing of each lead or lead position (N -1 places) from a, looking at the bottom of the package.

- N is the maximum number of terminal positions.

- Controlling dimension: millimeter.

SH-8 8-lead metal can package

|        | Millin | neters | Inc   |       |      |  |

|--------|--------|--------|-------|-------|------|--|

| Symbol | MIN    | MAX    | MIN   | MAX   | Note |  |

| Α      | 6.00   | 6.22   | 0.236 | 0.244 | _    |  |

| Øb     | 0.41   | 0.48   | 0.016 | 0.019 | 13   |  |

| Øb1    | 0.41   | 0.53   | 0.016 | 0.021 | 13   |  |

| Øb2    | 0.41   | 0.61   | 0.016 | 0.024 | -    |  |

| ØD     | 9.09   | 9.19   | 0.335 | 0.375 | -    |  |

| ØD1    | 8.23   | 8.43   | 0.305 | 0.335 | -    |  |

| Øe     | 0.2    | .00    | 5.    | -     |      |  |

| e1     | 0.1    | .00    | 2.    | -     |      |  |

| F      | 0.33   | 0.43   | 0.013 | 0.017 | _    |  |

| k      | 0.69   | 0.86   | 0.027 | 0.034 | -    |  |

| k1     | 0.69   | 1.14   | 0.027 | 0.045 | 14   |  |

| L      | 13.0   | 14.0   | 0.512 | 0.552 | 13   |  |

| L1     | _      | 1.27   | -     | 0.05  | 13   |  |

| L2     | 6.35   | 6.85   | 0.250 | 0.270 | 13   |  |

| Q      | 0.5    | )_     | 0.02  | -     | -    |  |

| α      | 4!     | 5°     | 4.    | 15    |      |  |

| β      | 45°    |        | 4.    | 15    |      |  |

| N      | 8      | 3      | 8     | 16    |      |  |

#### **Ordering Information**

| Part       | Mark.  | Temp.,<br>°C   | Package      | Package<br>Drawing |

|------------|--------|----------------|--------------|--------------------|

| FT101ASH5U | 101A5U | -60 to<br>+125 | 8-lead       |                    |

| FT201ASH5J | 201A5A | -40 to<br>+85  | metal<br>can | SH-8               |

| FT301ASH5U | 301A5J | 0 to<br>+70    |              |                    |

Notes :1. These Pb-free hermetic packaged products employ 100% Au plate, which is RoHS.

# **Revision History**

| Ũ⁄Ác     | ΔΩæΛ                        | Description |

|----------|-----------------------------|-------------|

| <u> </u> | <b>. Dæc</b> ?<br>20/405/13 | Original    |

|          | 20/03/13                    | Original    |

|          | 1                           |             |

|          |                             |             |

|          | 1                           |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

|          |                             |             |

Á Rev. 1

<sup>A</sup> Á Мау 2013

Ashley Crt, Henley, Marlborough, Wilts, SN8 3RH UK

Tel: +44(0)1264 731200 Fax:+44(0)1264 731444

E-mail: sales@forcetechnologies.co.uk

www.forcetechnologies.co.uk

Unless otherwise stated in this SCD/Data sheet, Force Technologies Ltd reserve the right to make changes, without notice, in the products, Includ -ing circuits, cells and/or software, described or contained herein in order to improve design and/or performance. Force Technologies resumes no responsibility or liability for the use of any of these products, conveys no licence or any title under patent, copyright, or mask work to these products, and makes no representation or warranties that these products are free from patent, copyright or mask work infringement, unless otherwise specified.

#### **Life Support Applications**

Force Technologies products are not designed for use in life support appliances, devices or systems where malfunction of a Force Technologies product can reasonably be expected to result in a personal injury. Force Technologies customers using or selling Force Technologies products for use in such applications do so at their own risk and agree to fully indemnify Force Technologies for any damages resulting from such improper use or sale.

This document is the property of Force Technologies Ltd not to be reproduced or implemented without the written permission of Force Technologies Ltd

All trademarks acknowledged

Copyright Force Technologies Ltd 2013