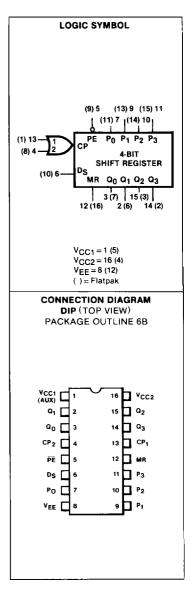

# F10000 4-BIT SHIFT REGISTER

**GENERAL DESCRIPTION** — The F10000 is a 4-Bit Parallel/Serial In, Parallel/Serial Out Shift Register. High Speed ECL technology permits storage, shifting, counting and serial code conversion at rates in excess of 200 MHz.

Features include assertion outputs for each stage, overriding asynchronous master reset, serial and parallel D type inputs and a gated clock. Availability of these features on one chip significantly improves the reliability, performance, and power consumption of high speed systems.

The F10000 incorporates a unique voltage compensation network which ensures that significant parameters such as logic levels, noise margins and speed remain constant over a wide range of power supply voltage.

- HIGH SPEED . . . 200 MHz TYPICAL SHIFT FREQUENCY

- D TYPE INPUTS SERIAL AND PARALLEL

- GATED CLOCK INPUT

- ASYNCHRONOUS MASTER RESET

- TERMINATED LINE DRIVE CAPABILITY

- WIRED-OR CAPABILITY

- SEPARATE VCC PINS ELIMINATE NOISE COUPLING

- 50 kΩ INPUT PULL DOWNS . . . UNUSED INPUTS MAY BE LEFT OPEN

- SINGLE VEE POWER SUPPLY . . . 4.7 V TO 6.2 V

- NOISE MARGINS INSENSITIVE TO POWER SUPPLY VARIATIONS AND GRADIENTS

#### PIN NAMES

| Pn      | Parallel Data Inputs                    |

|---------|-----------------------------------------|

| PE      | Parallel Enable (Active LOW)            |

| CPn     | Clock In, Shifts on Positive Transition |

| MR      | Asynchronous Master Reset—Active HIGH   |

| $D_{S}$ | Data Input, Serial                      |

| Qn      | Register Outputs                        |

|         |                                         |

### FAIRCHILD ECL DATA SHEET • F10000

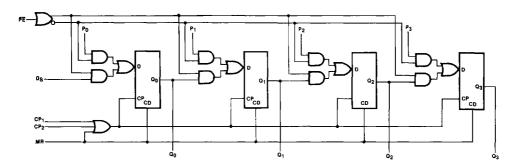

#### LOGIC DIAGRAM

Note that this diagram is provided for understanding of logic operation only. It should not be used for evaluation of propagation delays as many gate functions are achieved internally without incurring a full gate delay.

**FUNCTIONAL DESCRIPTION** — The F10000 is a high-speed 4-Bit Shift Register. It consists of four master/slave flip-flops and four 2-input multiplexers interconnected so as to permit loading of the masters from either a preceding slave output  $(Q_{n-1})$  or an external  $(P_n)$  input. The function desired is selected by the Parallel Enable (PE) input.

The masters are loaded during the LOW period of the clock (CP1, 2). As the clock changes from LOW to HiGH, the masters are inhibited from change followed by the enabling of the data path from master to slave. This data is then presented at the outputs ( $Q_n$ ). While the clock is HIGH, the masters are inhibited from change and the master/slave data path remains open. During the HIGH to LOW transition of the clock, the master/slave data path is inhibited. This is followed by the enabling of the masters for the acceptance of data from the parallel or serial logic inputs.

As the two clock inputs are ORed together, both must be LOW for the masters to accept new data. If either is raised to a HIGH, the register is clocked.

A HIGH on one Clock input can prevent the register from shifting, providing a hold condition. To prevent false triggering, this input must change from LOW to HIGH while the clock is HIGH.

The Master Reset (MR) function is asynchronous. When held HIGH, it overrides all other commands and forces all outputs  $(Q_n)$  LOW.

#### DC CHARACTERISTICS: VEE = -5.2 V, VCC = GND

| SYMBOL | CHARACTERISTIC                    |      | LIMITS |            | UNITS |      | CONDITIONS                               |

|--------|-----------------------------------|------|--------|------------|-------|------|------------------------------------------|

| STMBUL | CHARACTERISTIC                    | В    | TYP    | A          | UNIIS | TA   | CONDITIONS                               |

| IIH    | Input Current HIGH<br>MR (Pin 12) |      |        | 260<br>700 | μА    | 25°C | VIN = VIHA                               |

| IEE    | Power Supply Current              | - 85 | - 66   |            | mA    | 25°C | Outputs Open, Pin 4 or 13<br>Tied to VIH |

# FAIRCHILD ECL DATA SHEET • F10000

| 044001           | CHARACTERISTIC                                                      |     | LIMITS |     |       | CONDITIONS   |

|------------------|---------------------------------------------------------------------|-----|--------|-----|-------|--------------|

| SYMBOL           |                                                                     | В   | TYP    | A   | UNITS |              |

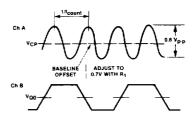

| fcount           | Shift Right Frequency                                               | 150 | 200    |     | MHz   | See Figure 3 |

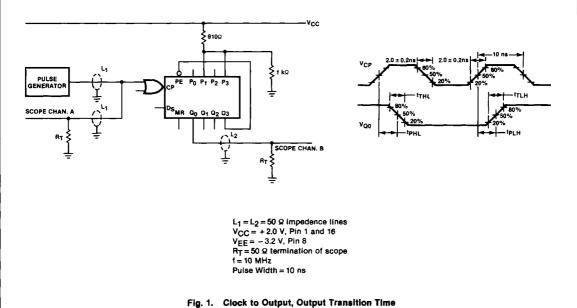

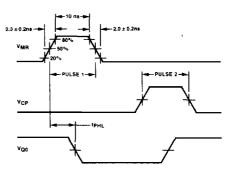

| <sup>t</sup> PLH | Propagation Delay<br>Clock to Output                                | 2.0 | 3.2    | 5.0 | ns    |              |

| <sup>t</sup> PHL | Propagation Delay<br>Clock to Output                                | 2.0 | 3.2    | 5.0 | ns    | See Figure 1 |

| t <sub>PHL</sub> | Propagation Delay<br>Master Reset to Output                         |     | 2.5    |     | ns    | See Figure 2 |

| tTLH             | Output Transition Time<br>LOW to HIGH (20% to 80%)                  | 1.3 | 2.0    | 3.5 | ns    |              |

| tTHL             | Output Transition Time<br>HIGH to LOW (80% to 20%)                  | 1.3 | 2.0    | 3.5 | ns    | See Figure 1 |

| tw               | Clock Pulse Width                                                   |     | 2.5    |     | ns    | See Figure 3 |

| t <sub>w</sub>   | MR Pulse Width                                                      |     | 3.5    |     | ns    |              |

| t <sub>s</sub>   | Set-Up Time Prior to Clock<br>DS to CP, Pn to CP                    | 1.5 | 0.5    |     | ns    |              |

| th               | Hold Time After Clock<br>D <sub>S</sub> to CP, P <sub>n</sub> to CP | 1.0 | - 0.5  |     | ns    |              |

| ts               | Set-Up Time Prior to Clock<br>PE to CP                              | 5.4 | 3.2    |     | ns    |              |

| th               | Hold Time After Clock PE to CP                                      | 0   | - 3.2  |     | ns    |              |

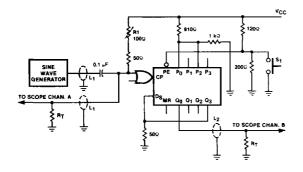

#### **SWITCHING CIRCUITS AND WAVEFORMS**

## **FAIRCHILD ECL DATA SHEET • F10000**

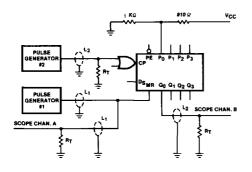

#### SWITCHING CIRCUIT AND WAVEFORMS (Cont'd)

L<sub>1</sub> = L<sub>2</sub> = 50  $\Omega$  impedance lines. V<sub>CC1</sub> = V<sub>CC2</sub> = +2.0 V V<sub>EE</sub> = -3.2 V R<sub>T</sub> = 50  $\Omega$  Termination of Scope f = 10 MHz Pulse 2  $\simeq$  Pulse 1

Fig. 2. Master Reset to Output

$\begin{array}{l} L_1=L_2=50~\Omega~impedance~lines\\ V_{CC1}=V_{CC2}=+2.0~V\\ R_T=50~\Omega~termination~of~scope\\ f=f_{MAX}\\ Load~the~register~by~closing~S_1 \end{array}$

Fig. 3. Shift Frequency