# Am93L01

## Low-Power Demultiplexer/One-of-Ten Decoder

### **Bistinctive Characteristics**

- 45 mw typical power dissipation.

- 50 ns typical propagation delay.

- 100% reliability assurance testing in compliance with MIL STD 883

- · Fan-out of three to standard TTL circuits.

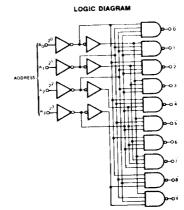

#### FUNCTIONAL DESCRIPTION

The Am93L01 low-power decoder accepts a tour-bit binary address and selects one-of-ten mutually exclusive active LOW outputs. The outputs are designated by the decimal equivalent of the binary code which selects them. Non-selected outputs are HIGH, and if the input code is greater than nine through the MIGH. all outputs are HIGH.

all outputs are riterin. Since codes greater than nine do not select any output, the SSL01 can be used as a one-of-eight decoder with an enable. The three-bit code is applied to inputs  $A_{\rm o}$ ,  $A_{\rm i}$ , and  $A_{\rm o}$ . If  $A_{\rm i}$  is LOW, one of the outputs 0 through 7 will go LOW; if  $A_{\rm i}$  is HGH, then either output 8 or 9, or none of the outputs will set LOW. Hence Input A. becomes an active LOW enable for ritish, then either output 8 or 9, or none of the outputs will go LOW. Hence, input A, becomes an active LOW enable for a one-of-eight decoder. The device can also be used as a demultiplexer by applying data to input A, and an address to inputs A<sub>a</sub>, A<sub>i</sub>, and A<sub>b</sub>. The addressed output will follow the data on A.

#### LOADING RULES In Unit Loads (Notes)

| 1114          | O    |      |           |     |  |

|---------------|------|------|-----------|-----|--|

|               | TTL  | oads | 93L loads |     |  |

| Input loading | HIGH | LOW  | HIGH      | LOW |  |

| Ali Inputs    | 0.5  | 0.25 | 1.0       | 1.0 |  |

| Output Drive  | HIGH | LOW  | HIGH      | LOW |  |

| All Outputs   | 10   | 3    | 12        | 12  |  |

- 1) A TTL unit load is specified as 0.4 V at -1.8 mA LOW, 2.4 V at 40  $\mu$ A HIGH. 2) A 83L unit load is specified as 0.3 V at -400  $\mu$ A LOW, 2.4 V at 20  $\mu$ A HIGH.

- HIGH. 3 Rough output LOW current is available to mix TTL and 93L loads and still meet the 93L requirement of a  $V_{\rm OL}$  of 0.3 V.

#### LOGIC SYMBOL

- PIN 16 GND - PIN 8

#### Amesica ORDERING INFORMATION

Package Туре 16-Pin Molded DIP 16-Pin Hermetic DIP 16-Pin Hermetic DIP 16-Pin Hermetic DIP 16-Pin Hermetic Flater

Temperatura formation

Order 125°C C to +125°

U6M93L0159X 117B93L0159X U7B93L0151X LIXX93L01XXD

Note: The dice supplied will contain units which meet both 6°C to +75°C and -55°C to +125°C temperature ranges.

MAXIMUM RATINGS (Above which the useful life may be impaired)

-65°C to +150°C Storage Temperature - 55°C to + 125°C Temperature (Ambient) Under Bias Supply Voltage to Ground Potential (Pin 15 to Pin 8) Continuous -0.5 V to +7 V

-0.5 V to +V \_ max DC Voltage Applied to Outputs for High Output State -0.5 V to +5.5 V OC Input Voltage

Output Current, Into Outputs -30 mA to +5.0 mA DC input Current (Note 1)

Note 1. Maximum current defined by DC input voltage

30 mA

ELECTRIC: ARACTERISTICS OVER OPERATING TEMPERATURE RANGE (Unless Otherwise Noted)

| Parameters                  | Description                         | Test Conditions                                                                     | Min. | Typ. (Note 1) | Max. | Units |

|-----------------------------|-------------------------------------|-------------------------------------------------------------------------------------|------|---------------|------|-------|

| V <sub>OH</sub>             | Output HIGH Voltage                 | $V_{CC} = MIN., I_{OH} = -0.4 \text{ mA}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$   | 2.4  | 3.6           |      | Vois  |

| Vol                         | Output LOW Voltage                  | $V_{fC} = MIN$ , $I_{OL} = 4.92 \text{ mA}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ |      | 0.15          | 0.3  | Volta |

| V <sub>IH</sub>             | Input HIGH Level                    | Guaranteed Input logical HIGH voltage for all inputs                                | 2.0  |               |      | Volts |

| V <sub>IL</sub>             | Input LOW Level                     | Guaranteed input logical LOW voltage for all inputs                                 |      |               | 0.7  | Voiu  |

| l <sub>IL</sub><br>(Note 2) | 93L Unit Load<br>Input LOW Current  | $V_{CC} = MAX., V_{IN} = 0.3 V$                                                     |      | -0.25         | -0.4 | mA    |

| i <sub>jH</sub><br>(Note 2) | 93L Unit Load<br>Input HIGH Current | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.4 V                                     |      | 2.0           | 20   | μА    |

|                             | Input HIGH Current                  | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 5.5 V                                     |      |               | 1.0  | mA    |

| I <sub>sc</sub>             | Output Short Circuit Current        | V <sub>CC</sub> = MAX., V <sub>QUI</sub> = 0.0 V                                    | -2.5 | -16           | -25  | mÁ    |

| lcc                         | Power Supply Current                | V <sub>CC</sub> = MAX.                                                              |      | 9.0           | 13   | mA    |

Notes: 1) Typical limits are at  $V_{\rm CC} = 5.0 \, \text{V}$ , 25°C ambient and maximum loading.

2) Actual input currents are obtained by multiplying unit load current by the 93L input load factor. (See loading rules)

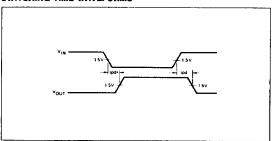

#### SWITCHING CHARACTERISTICS (7. - 25°C)

| Parameters        | Description                  | Test Conditions         | Min. | Тур. | Max. | Units |

|-------------------|------------------------------|-------------------------|------|------|------|-------|

| t <sub>pd+</sub>  | Delay Address to Output HIGH | V <sub>CC</sub> = 5.0 V | 20   | 48   | 65   | ns    |

| t <sub>pd</sub> _ | Delay Address to Output LOW  | C <sub>L</sub> = 15 pF  | 20   | 50   | 70   | ns    |

oleel.

#### **SWITCHING TIME WAVEFORMS**

ADVANCEI MICR DEVICES INC 901 Thompson Plac Sunnyval California 9408 (408) 732-240 TWX: 910-339-928 TELEX: 34-630

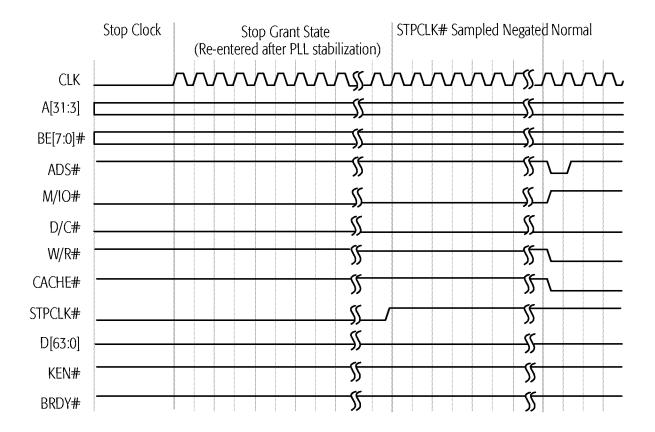

Figure 75. Stop Grant and Stop Clock Modes, Part 2

21850E/0-November 1998

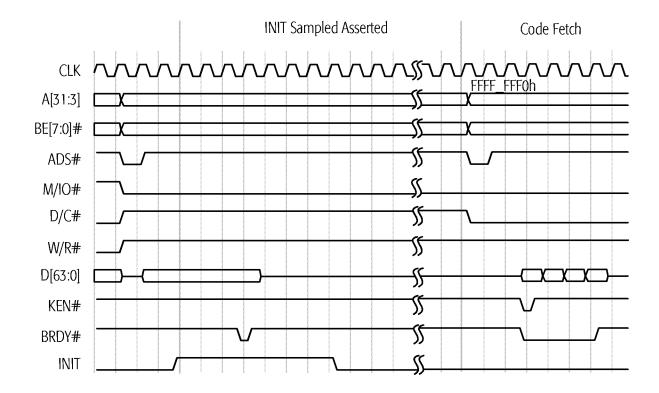

# INIT-Initiated Transition from Protected Mode to Real Mode

INIT is typically asserted in response to a BIOS interrupt that writes to an I/O port. This interrupt is often in response to a Ctrl-Alt-Del keyboard input. The BIOS writes to a port (similar to port 64h in the keyboard controller) that asserts INIT. INIT is also used to support 80286 software that must return to Real mode after accessing extended memory in Protected mode.

The assertion of INIT causes the processor to empty its pipelines, initialize most of its internal state, and branch to address FFFF\_FFF0h—the same instruction execution starting point used after RESET. Unlike RESET, the processor preserves the contents of its caches, the floating-point state, the MMX state, Model-Specific Registers (MSRs), the CD and NW bits of the CR0 register, the time stamp counter, and other specific internal resources.

Figure 76 shows an example in which the operating system writes to an I/O port, causing the system logic to assert INIT. The sampling of INIT asserted starts an extended microcode sequence that terminates with a code fetch from FFFF\_FFFOh, the reset location. INIT is sampled on every clock edge but is not recognized until the next instruction boundary. During an I/O write cycle, it must be sampled asserted a minimum of three clock edges before BRDY# is sampled asserted if it is to be recognized on the boundary between the I/O write instruction and the following instruction. If INIT is asserted synchronously, it can be asserted for a minimum of one clock. If it is asserted asynchronously, it must have been negated for a minimum of two clocks, followed by an assertion of a minimum of two clocks.

Figure 76. INIT-Initiated Transition from Protected Mode to Real Mode

21850E/0-November 1998

# 6 Power-on Configuration and Initialization

On power-on the system logic must reset the AMD-K6-2 processor by asserting the RESET signal. When the processor samples RESET asserted, it immediately flushes and initializes all internal resources and its internal state, including its pipelines and caches, the floating-point state, the MMX and 3DNow! states, and all registers. Then the processor jumps to address FFFF FFF0h to start instruction execution.

## 6.1 Signals Sampled During the Falling Transition of RESET

FLUSH#

FLUSH# is sampled on the falling transition of RESET to determine if the processor begins normal instruction execution or enters Tri-State Test mode. If FLUSH# is High during the falling transition of RESET, the processor unconditionally runs its Built-In Self Test (BIST), performs the normal reset functions, then jumps to address FFFF\_FFF0h to start instruction execution. (See "Built-In Self-Test (BIST)" on page 217 for more details.) If FLUSH# is Low during the falling transition of RESET, the processor enters Tri-State Test mode. (See "Tri-State Test Mode" on page 218 and "FLUSH# (Cache Flush)" on page 103 for more details.)

**BF[2:0]**

The internal operating frequency of the processor is determined by the state of the bus frequency signals BF[2:0] when they are sampled during the falling transition of RESET. The frequency of the CLK input signal is multiplied internally by a ratio defined by BF[2:0]. (See "BF[2:0] (Bus Frequency)" on page 92 for the processor-clock to bus-clock ratios.)

**BRDYC#**

BRDYC# is sampled on the falling transition of RESET to configure the drive strength of A[20:3], ADS#, HITM#, and W/R#. If BRDYC# is Low during the fall of RESET, these outputs are configured using higher drive strengths than the standard strength. If BRDYC# is High during the fall of RESET, the standard strength is selected. (See "BRDYC# (Burst Ready Copy)" on page 95 for more details.)

21850E/0-November 1998

## **6.2 RESET Requirements**

During the initial power-on reset of the processor, RESET must remain asserted for a minimum of 1.0 ms after CLK and  $V_{CC}$  reach specification. (See "CLK Switching Characteristics" on page 255 for clock specifications. See "Electrical Data" on page 247 for  $V_{CC}$  specifications.)

During a warm reset while CLK and  $V_{\rm CC}$  are within specification, RESET must remain asserted for a minimum of 15 clocks prior to its negation.

## 6.3 State of Processor After RESET

## **Output Signals**

Table 31 shows the state of all processor outputs and bidirectional signals immediately after RESET is sampled asserted.

**Table 31. Output Signal State After RESET**

| Signal           | State    | Signal   | State    |

|------------------|----------|----------|----------|

| A[31:3], AP      | Floating | LOCK#    | High     |

| ADS#, ADSC#      | High     | M/IO#    | Low      |

| APCHK#           | High     | PCD      | Low      |

| BE[7:0]#         | Floating | PCHK#    | High     |

| BREQ             | Low      | PWT      | Low      |

| CACHE#           | High     | SCYC     | Low      |

| D/C#             | Low      | SMIACT#  | High     |

| D[63:0], DP[7:0] | Floating | TDO      | Floating |

| FERR#            | High     | VCC2DET  | Low      |

| HIT#             | High     | VCC2H/L# | Low      |

| HITM#            | High     | W/R#     | Low      |

| HLDA             | Low      | -        | -        |

## **Registers**

Table 32 on page 175 shows the state of all architecture registers and Model-Specific Registers (MSRs) after the processor has completed its initialization due to the recognition of the assertion of RESET.