# 54F/74F674 16-Bit Serial/Parallel-In, Serial-Out Shift Register

## **General Description**

The 'F674 is a 16-bit shift register with serial and parallel load capability and serial output. A single pin serves alternately as an input for serial entry or as a TRI-STATE® serial output. In the serial-out mode the data recirculates in the register. Chip Select, Read/Write and Mode inputs provide control flexibility.

### **Features**

- 16-Bit serial I/O shift register

- 16-Bit parallel-in, serial-out converter

- Recirculating serial shifting

- Common serial data I/O pin

- Slim 24 lead DIP

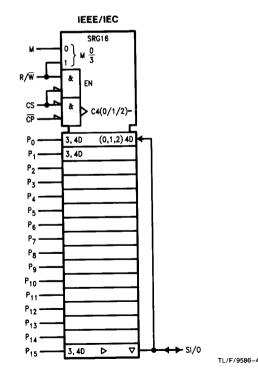

## **Logic Symbols**

# CS P<sub>0</sub> P<sub>1</sub> P<sub>2</sub> P<sub>3</sub> P<sub>4</sub> P<sub>5</sub> P<sub>6</sub> P<sub>7</sub> P<sub>8</sub> P<sub>9</sub> P<sub>10</sub> P<sub>11</sub> P<sub>12</sub> P<sub>13</sub> P<sub>14</sub> P<sub>15</sub> CP R/W M SI/O

TL/F/9586-1

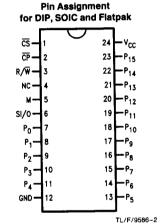

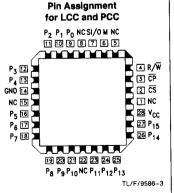

## **Connection Diagrams**

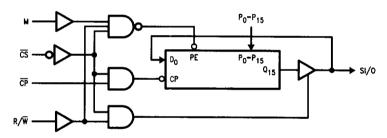

## **Functional Description**

The 16-bit shift register operates in one of four modes, as indicated in the Shift Register Operations Table.

Hold—a HIGH signal on the Chip Select ( $\overline{\text{CS}}$ ) input prevents clocking and forces the Serial Input/Output (SI/O) TRI-STATE buffer into high impedance state.

Serial Load—data present on the SI/O pin shifts into the register on the falling edge of  $\overline{CP}$ . Data enters the  $Q_0$  position and shifts toward  $Q_{15}$  on successive clocks.

Serial Output—the SI/O TRI-STATE buffer is active and the register contents are shifted out from Q<sub>15</sub> and simultaneously shifted back into Q<sub>0</sub>.

Parallel Load—data present on  $P_0$ - $P_{15}$  are entered into the register on the falling edge of  $\overline{CP}$ . The SI/O TRI-STATE buffer is active and represents the  $Q_{15}$  output.

To prevent false clocking,  $\overline{CP}$  must be LOW during a LOW-to-HIGH transition of  $\overline{CS}$ .

**Shift Register Operations Table**

| Control Inputs |        |        |    | SI/O              | Operating Mode                      |

|----------------|--------|--------|----|-------------------|-------------------------------------|

| <u>cs</u>      | R/W    | M      | CP | Status            | Operating mode                      |

| H<br>L         | X<br>L | X<br>X | ×  | High Z<br>Data In | Hold<br>Serial Load                 |

| L              | Н      | L      | ~  | Data Out          | Serial Output<br>with Recirculation |

| L              | Н      | Н      | ~  | Active            | Parallel Load;<br>No Shifting       |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= HIGH-to-LOW Transition

## **Block Diagram**

TL/F/9586-5