# Recent Additions CD54AC109/3A CD54ACT109/3A

# **Dual "J-K" Flip-Flop with Set and Reset**

Positive-Edge-Triggered (J, K)

The RCA CD54AC109 and CD54ACT109 are dual "J-K" flip-flops with set and reset that utilize the new RCA ADVANCED CMOS LOGIC technology. These flip-flops have independent J, K, Set, Reset, and Clock inputs and Q and Q outputs. The CD54AC/ACT109 changes state on the positive-going transition of the clock. Set and Reset are accomplished asynchronously by low-level inputs.

The CD54AC109 and CD54ACT109 are supplied in 16-lead dual-in-line ceramic packages (F suffix).

## **Package Specifications**

(See Section 11, Fig. 11)

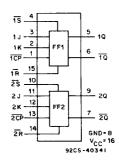

**FUNCTIONAL DIAGRAM**

### Static Electrical Characteristics (Limits with black dots (•) are tested 100%.)

|                                                  | TEST CONDITIONS              |                        | V <sub>cc</sub> | AMBIENT TEMPERATURE (TA) - °C |      |             |      |       |

|--------------------------------------------------|------------------------------|------------------------|-----------------|-------------------------------|------|-------------|------|-------|

| CHARACTERISTICS                                  |                              |                        |                 | +25                           |      | -55 to +125 |      | UNITS |

|                                                  | V,<br>(V)                    | l <sub>o</sub><br>(mA) | (V)             | MIN.                          | MAX. | MIN.        | MAX. |       |

| Quiescent Supply<br>Current (FF) I <sub>CC</sub> | V <sub>CC</sub><br>or<br>GND | 0                      | 5.5             | _                             | 4•   | l           | 80•  | μΑ    |

The complete static electrical test specification consists of the above by-type static tests combined with the standard static tests in the beginning of this section.

#### **ACT INPUT LOADING TABLE**

| INPUT     | UNIT LOAD* |

|-----------|------------|

| J, CP, CP | 1          |

| ĸ         | 0.53       |

| Ŝ, Ŕ      | 0.58       |

\*Unit load is  $\Delta I_{CC}$  limit specified in Static Characteristics Chart, e.g., 2.4 mA max. @ 25° C.

### **Burn-In Test-Circuit Connections**

Identical to CD54HC/HCT109/3A, page 5-43.

# Recent Additions CD54AC109/3A CD54ACT109/3A

### SWITCHING CHARACTERISTICS: AC Series; t,, t, = 3 ns, C, = 50 pF (Worst Case)

| CHARACTERISTICS                        | SYMBOL                               | V <sub>cc</sub><br>(V) | -55 to         |                      |       |

|----------------------------------------|--------------------------------------|------------------------|----------------|----------------------|-------|

|                                        |                                      |                        | MIN.           | MAX.                 | UNITS |

| Propagation Delays:<br>CP (CP) to Q, Q | t <sub>PLH</sub><br>t <sub>PHL</sub> | 1.5<br>3.3*<br>5†      | <br>2.7<br>1.7 | 129<br>14.4<br>10.3• | ns    |

| S, R to Q, Q                           | t <sub>PLH</sub><br>t <sub>PHL</sub> | 1.5<br>3.3<br>5        |                | 153<br>17.1<br>12.2• | ns    |

| Power Dissipation Capacitance          | C <sub>PD</sub> §                    |                        |                |                      | pF    |

| Input Capacitance                      | Cı                                   | _                      | _              | 10                   | pF    |

### SWITCHING CHARACTERISTICS: ACT Series; t,, t, = 3 ns, C, = 50 pF (Worst Case)

|                                        |                   | Vcc | -55 to |       |       |

|----------------------------------------|-------------------|-----|--------|-------|-------|

| CHARACTERISTICS                        | SYMBOL            | (V) | MIN.   | MAX.  | UNITS |

| Propagation Delays:<br>CP (CP) to Q, Q | t <sub>PLH</sub>  | 5†  | 1.7    | 10.3• | ns    |

| S, R, to Q, Q                          | t <sub>PHL</sub>  | 5   | 2.3    | 13.5∙ | ns    |

| Power Dissipation Capacitance          | C <sub>PD</sub> § | _   |        |       | pF    |

| Input Capacitance                      | Cı                | _   |        | 10    | pF    |

\*3.3 V: min. is @ 3.6 V max. is @ 3 V  $\ensuremath{\S{C_{PD}}}$  is used to determine the dynamic power consumption per flip-flop.

For AC,  $P_D = C_{PD}V_{CC}^2 f_i + \Sigma (C_LV_{CC}^2 f_o)$

†5 V: min. is @ 5.5 V

For ACT,  $P_D$  =  $C_{PD}V_{CC}{}^2$   $f_i$  +  $\Sigma$  ( $C_LV_{CC}{}^2$   $f_o$ ) +  $V_{CC}$   $\Delta I_{CC}$  where  $f_i$  = input frequency

fo = output frequency

max. is @ 4.5 V

C<sub>L</sub> = output load capacitance

V<sub>CC</sub> = supply voltage

(Limits with black dots (•) are tested 100%.)

## CD54AC112/3A CD54ACT112/3A

# **Dual "J-K" Flip-Flop with Set and Reset**

Negative-Edge-Triggered (J, K)

The RCA CD54AC112 and CD54ACT112 are dual "J-K" flip-flops with set and reset that utilize the new RCA ADVANCED CMOS LOGIC technology. These flip-flops have independent J, K, Set, Reset, and Clock inputs and Q and Q outputs. The CD54AC/ACT112 changes state on the negative-going transition of the clock pulse. Set and Reset are accomplished asynchronously by low-level inputs.

The CD54AC112 and CD54ACT112 are supplied in 16-lead dual-in-line ceramic packages (F suffix).

## **Package Specifications**

(See Section 11, Fig. 11)

**FUNCTIONAL DIAGRAM**