# Am2919

Quad Register with Dual Three-State Outputs

#### DISTINCTIVE CHARACTERISTICS

- Four D-type flip-flops

- Two sets of three-state outputs

- · Polarity control on one set of outputs

- Buffered common clock enable

- Buffered common asynchronous clear

- Separate buffered common output enable for each set of outputs

#### **GENERAL DESCRIPTION**

The Am2919 consists of four D-type flip-flops with a buffered common clock enable. Information meeting the set-up and hold time requirements of the D inputs is transferred to the flip-flop outputs on the LOW-to-HIGH transition of the clock. Data on the Q outputs of the flip-flops is enabled at the three-state outputs when the output control ( $\overline{OE}$ ) input is LOW. When the appropriate  $\overline{OE}$  input is HIGH, the outputs are in the high impedance state. Two independent sets of outputs—W and Y—are provided such

that the register can simultaneously and independently drive two buses. One set of outputs contains a polarity control such that the outputs can either be inverting or non-inverting.

The device also features an active LOW asynchronous clear. When the clear input is LOW, the Q output of the Internal flip-flops are forced LOW independent of the other inputs. The Am2919 is packaged in a space-saving (0.3-inch row spacing) 20-pin package.

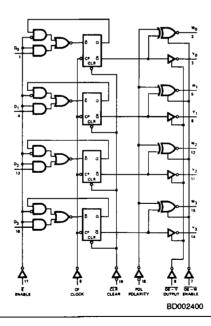

#### **BLOCK DIAGRAM**

#### **RELATED PRODUCTS**

| Part No.   | Description     |  |  |  |

|------------|-----------------|--|--|--|

| Am25LS2519 | Quad Register   |  |  |  |

| Am25LS2518 | Quad D Register |  |  |  |

03597B

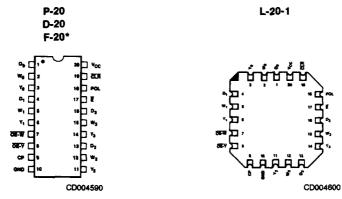

# CONNECTION DIAGRAM Top View

\*F-20 pin configuration identical to D-20, P-20.

Note: Pin 1 is marked for orientation

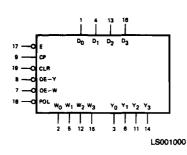

#### LOGIC SYMBOL

#### **ORDERING INFORMATION**

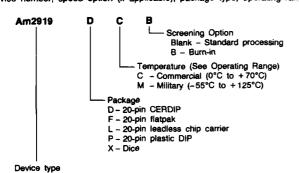

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

**Quad Register**

| Valid Combinations |                                                                       |  |  |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|--|--|

| Am2912             | PC<br>DC, DCB, DM,<br>DMB<br>FM, FMB<br>LC, LCB, LM,<br>LMB<br>XC, XM |  |  |  |  |

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

#### PIN DESCRIPTION

| Pin No.         | Name       | 1/0 | Description                                                                                                                                                                                                                                                  |

|-----------------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 13,<br>16 | Di         | 1   | Any of the four D flip-flop data lines.                                                                                                                                                                                                                      |

| 17              | Ε          | ı   | Clock Enable. When LOW, the data is entered into the register on the next clock LOW-to-HIGH transition. When HIGH, the data in the register remains unchanged, regardless of the data in.                                                                    |

| 9               | CP         | 1   | Clock Pulse. Data is entered into the register on the LOW-to-HIGH transition.                                                                                                                                                                                |

| 7, 8            | OE-W, OE-Y | 1   | Output Enable. When $\overline{\text{OE}}$ is LOW, the register is enabled to the output. When HIGH, the output is in the high-impedance state. The $\overline{\text{OE-W}}$ controls the W set of outputs, and $\overline{\text{OE-Y}}$ controls the Y set. |

| 3, 6, 11,<br>14 | Υ,         | 0   | Any of the four non-inverting three-state output lines.                                                                                                                                                                                                      |

| 2, 5, 12,<br>15 | Wi         | 0   | Any of the four three-state outputs with polarity control.                                                                                                                                                                                                   |

| 18              | POL        | i   | Polarity Control. The W <sub>i</sub> outputs will be non-inverting when POL is LOW, and when it is HIGH, the outputs are inverting.                                                                                                                          |

| 19              | CLR        | 11  | Asynchronous Clear. When CLR is LOW, the internal Q flip-flops are reset to LOW.                                                                                                                                                                             |

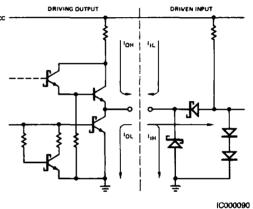

# GUARANTEED LOADING RULES OVER OPERATING RANGE (In Unit Loads)

A Low-Power Schottky TTL Unit Load is defined as 20μA measured at 2.7V HIGH and -0.36mA measured at 0.4V LOW.

| Pin   | Input/         | Input | Output<br>HIGH |              |     | utput<br>.OW |

|-------|----------------|-------|----------------|--------------|-----|--------------|

| No.'s | Output         | Load  | MIL            | COM'L        | MIL | COMIL        |

| 1     | D <sub>0</sub> | 1.0   |                | -            | -   | -            |

| 2     | $\mathbf{w}_0$ | -     | 50             | 130          | 33  | 33           |

| 3     | Yo             | -     | 50             | 130          | 33  | 33           |

| 4     | D <sub>1</sub> | 1.0   | _              | <del>-</del> | -   | -            |

| 5     | W <sub>1</sub> | -     | 50             | 130          | 33  | 33           |

| 6     | Y <sub>1</sub> | -     | 50             | 130          | 33  | 33           |

| 7     | OE-W           | 1.0   | -              | _            | -   | _            |

| 8     | OE-Y           | 1.0   | -              | -            | -   | -            |

| 9     | CP             | 1.0   | -              | -            | _   | -            |

| 10    | GND            | -     | -              | -            | _   | _            |

| 11    | Y <sub>2</sub> |       | 50             | 130          | 33  | 33           |

| 12    | W <sub>2</sub> |       | 50             | 130          | 33  | 33           |

| 13    | D <sub>2</sub> | 1.0   | ~              | _            | _   | -            |

| 14    | Y3             | -     | 50             | 130          | 33  | 33           |

| 15    | W <sub>3</sub> |       | 50             | 130          | 33  | 33           |

| 16    | D <sub>3</sub> | 1.0   | _              | -            | _   | -            |

| 17    | Ē              | 1.0   | ~              | -            |     | _            |

| 18    | POL            | 1.0   |                | -            | _   |              |

| 19    | CLR            | 1.0   | -              | -            |     |              |

| 20    | Vcc            |       | _              | -            | _   | _            |

# LOW-POWER SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

| FUNCTION TABLE             |             |        |             |             |             |             |             |                      |                              |                                   |  |

|----------------------------|-------------|--------|-------------|-------------|-------------|-------------|-------------|----------------------|------------------------------|-----------------------------------|--|

| Function                   |             | Inputs |             |             |             |             |             | Internal             | Outputs                      |                                   |  |

|                            | СР          | Dı     | Ē           | CLR         | POL         | ŌE-W        | ŌE-Y        | Q                    | Wi                           | Yi                                |  |

| Output Three-State Control | X<br>X<br>X | ×××    | X<br>X<br>X | X<br>X<br>X | X<br>X<br>X | HLHL        | HHL         | NC<br>NC<br>NC<br>NC | Z<br>Enabled<br>Z<br>Enabled | Enabled<br>Z<br>Z<br>Z<br>Enabled |  |

| W <sub>i</sub> Polarity    | X           | X      | X           | X<br>X      | H           | L<br>L      | L<br>L      | NC<br>NC             | Non-Inverting<br>Inverting   | Non-Inverting<br>Non-Inverting    |  |

| Asynchronous Clear         | X           | X      | X           | L           | LH          | L           | L<br>L      | L<br>L               | L<br>H                       | L                                 |  |

| Clock Enabled              | + + +       | IICLX  | Hurri       | 1111        | XLHLH       | X<br>L<br>L | X<br>L<br>L | NC<br>L<br>H<br>H    | NC<br>L<br>H<br>H            | NC<br>L<br>H<br>H                 |  |

L = LOW H = HIGH

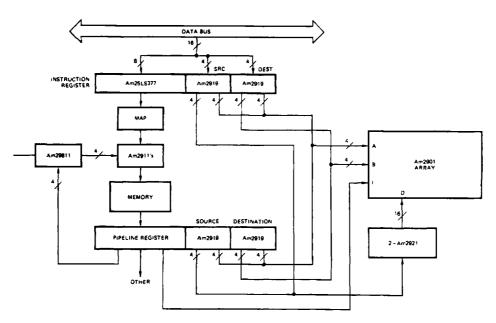

#### **APPLICATION**

AF001850

The Am2919 provides for easy control of the selection of source and destination register addresses for the Am2901. These controls can emanate from both the instruction register and the pipeline register. The control is accomplished by three-state action at the Am2919 outputs. Four different register outputs can be selected by the B address which is the destination register in the Am2901. Two registers can be selected for the Am2901 A input which is a second RAM source.

The other pair of three-state outputs can be used for function control select as shown with the Am2921. Here, bit set, bit clear, bit toggle and bit test on any of the 16 bits can be performed.

Z = High Impedance NC = No Change

X = Don't Care

t = LOW-to-HIGH Transition

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C (Ambient) Temperature Under Bias55°C to +125°C |

|----------------------------------------------------------------------------------|

| Supply Voltage to Ground Potential                                               |

| Continuous0.5V to +7.0V                                                          |

| DC Voltage Applied to Outputs For                                                |

| High Output State0.5V to + V <sub>CC</sub> max                                   |

| DC Input Voltage0.5V to +7.0V                                                    |

| DC Output Current, Into Outputs                                                  |

| DC Input Current30mA to +5.0mA                                                   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices                                                        |                    |

|-------------------------------------------------------------------------------|--------------------|

| Temperature                                                                   | 0°C to +70°C       |

| Supply Voltage+                                                               | 4.75V to +5.25V    |

| Military (M) Devices                                                          |                    |

| Temperature                                                                   | 55°C to +125°C     |

| Supply Voltage                                                                | +4.5V to $+5.5V$   |

| Operating ranges define those limits over wality of the device is guaranteed. | hich the function- |

DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                              | Test Con                                        | Test Conditions (Note 2)                             |       |     |       | Max   | Units |

|-----------------|------------------------------------------|-------------------------------------------------|------------------------------------------------------|-------|-----|-------|-------|-------|

|                 | _                                        | V <sub>CC</sub> = MIN                           | MIL, I <sub>OH</sub> = ~1.0m                         | A     | 2.4 | 3.4   |       |       |

| VOH             | Output HIGH Voltage                      | VIN = VH or VIL                                 | COM'L, IOH = -2.                                     | 6mA   | 2.4 | 3.4   |       | Volts |

|                 |                                          |                                                 | I <sub>OL</sub> = 4.0mA                              |       |     |       | 0.4   |       |

| VOL             | Output LOW Voltage                       | V <sub>CC</sub> = MIN,                          | I <sub>OL</sub> = 8.0mA                              |       |     |       | 0.45  | Volts |

| -OL             |                                          | VIN = VIH or VIL                                | I <sub>OL</sub> = 12mA                               |       |     |       | 0.5   | 1     |

| VIH             | Input HiGH Level                         | Guaranteed input logical voltage for all inputs | Guaranteed input logical HIGH voltage for all inputs |       |     |       |       | Volts |

|                 |                                          | Guaranteed input logical                        | al LOW                                               | MIL   |     |       | 0.7   | Volts |

| V <sub>IL</sub> | Input LOW Level                          | voltage for all inputs                          |                                                      | COM'L |     |       | 0.8   |       |

| Vi              | Input Clamp Voltage                      | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18m   | A                                                    |       |     |       | -1.5  | Volts |

| IĮL             | Input LOW Current                        | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4V   | 1                                                    |       |     |       | ~0.36 | mA    |

| l <sub>IH</sub> | Input HIGH Current                       | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7V   | 1                                                    |       |     |       | 20    | μA    |

| lį              | Input HIGH Current                       | VCC = MAX, VIN = 7.0V                           | •                                                    |       |     |       | 0.1   | mA    |

|                 | Off-State (High-Impedance)               |                                                 | V <sub>O</sub> = 0.4V                                |       |     | , and | -20   |       |

| ю               | Output Current                           | V <sub>CC</sub> = MAX                           | V <sub>O</sub> = 2.4V                                |       |     |       | 20    | μА    |

| Isc             | Output Short Circuit Current<br>(Note 3) | V <sub>CC</sub> = MAX                           | V <sub>CC</sub> = MAX                                |       |     |       | -85   | mA    |

| · · ·           | Power Supply Current                     |                                                 |                                                      | MIL   |     | 24    | 36    |       |

| Icc             | (Note 4)                                 | V <sub>CC</sub> = MAX                           |                                                      | COM'L |     | 24    | 39    | mA    |

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. Inputs grounded: outputs open.

## SWITCHING CHARACTERISTICS (TA = +25°C, VCC = 5.0V)

| Parameters            | Descripti                                       | on          | Test Conditions                 | Min | Тур | Max | Units |

|-----------------------|-------------------------------------------------|-------------|---------------------------------|-----|-----|-----|-------|

| t <sub>PHL</sub>      | Clock to Yi                                     |             |                                 |     | 22  | 33  |       |

| t <sub>PHL</sub>      | Clock to 11                                     |             |                                 |     | 20  | 30  | ns    |

| t <sub>PLH</sub>      | Clock to Wi                                     |             |                                 |     | 24  | 36  |       |

| t <sub>PHL</sub>      | (Either Polarity)                               |             |                                 |     | 24  | 36  | ns    |

| tPHL                  | Clear to Yi                                     |             |                                 |     | 29  | 43  | ns    |

| tPLH                  | Clear to Wi                                     |             |                                 |     | 25  | 37  |       |

| tphL                  | Clear to vv,                                    |             |                                 |     | 30  | 45  | ns    |

| t <sub>PLH</sub>      | Polarity to Wi                                  |             |                                 |     | 23  | 34  |       |

| t <sub>PHL</sub>      | Polarity to Wi                                  |             | C <sub>L</sub> = 15pF           |     | 25  | 37  | ns    |

| t <sub>pw</sub>       | Clear                                           |             | R <sub>L</sub> = 2.0kΩ          | 18  |     |     | ns    |

| tow Clock Pulse Width | LOW                                             |             | 15                              |     |     |     |       |

| t <sub>pw</sub>       | Glock Pulse Width                               | HIGH        |                                 | 18  |     |     | ns    |

| ts                    | Data                                            | -           |                                 | 15  |     |     | ns    |

| th                    | Data                                            |             |                                 | 5   |     |     | ns    |

| t <sub>8</sub>        | Data Enable                                     |             |                                 | 20  |     |     | ns    |

| th                    | Data Enable                                     |             |                                 | 0   |     |     | ns    |

| ts                    | Set-up Time, Clear<br>Recovery (Inactive) to Cl | ock         |                                 | 20  | 15  |     | ns    |

| <sup>t</sup> zH       | Output Enable to W or                           |             |                                 |     | 11  | 17  |       |

| tzL                   | Output Enable to W or Y                         |             |                                 |     | 13  | 20  | ns    |

| tHZ                   | Output Enable to W or                           | ,           | C <sub>L</sub> = 5.0pF          |     | 13  | 20  | ne    |

| t <sub>LZ</sub>       | Output Enable to W or                           |             | $R_L = 2.0k\Omega$              |     | 11  | 17  | ns    |

| f <sub>max</sub>      | Maximum Clock Frequence                         | cy (Note 1) | $C_L = 15pF$ $R_L = 2.0k\Omega$ | 35  | 45  |     | MHz   |

Note 1. Per industry convention, f<sub>max</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>r</sub>, t<sub>f</sub>, pulse width or duty cycle.

### SWITCHING CHARACTERISTICS over operating range unless otherwise specified\*

|                  |                                                   |                            |                                                 | Comr | nercial | MH  | tary |       |

|------------------|---------------------------------------------------|----------------------------|-------------------------------------------------|------|---------|-----|------|-------|

|                  |                                                   |                            | Am2919                                          |      | 2919    | Am  | 2919 | ĺ     |

| Parameters       | Description                                       |                            | Test Conditions                                 | Min  | Max     | Min | Max  | Units |

| t <sub>PLH</sub> | Clock to Yi                                       |                            | _                                               |      | 39      |     | 42   |       |

| <sup>t</sup> PHL | Clock to 1                                        |                            |                                                 |      | 39      |     | 45   | ns    |

| <b>t</b> PLH     | Clock to Wi                                       |                            |                                                 |      | 41      |     | 43   |       |

| <sup>t</sup> PHL | (Either Polarity)                                 |                            |                                                 |      | 44      |     | 48   | ns    |

| <sup>t</sup> PHL | Clear to Yi                                       |                            |                                                 |      | 52      |     | 58   | ns    |

| tрцн             | Clear to Wi                                       |                            |                                                 |      | 42      |     | 43   |       |

| <sup>t</sup> PHL |                                                   |                            |                                                 |      | 51      |     | 53   | ns    |

| t <sub>PLH</sub> | Polarity to Wi                                    |                            |                                                 |      | 41      |     | 45   |       |

| t <sub>PHL</sub> | Folanty to Wi                                     |                            | C <sub>L</sub> = 50pF                           |      | 42      |     | 44   | ns    |

| tpw              | Clear                                             |                            | $R_L = 2.0k\Omega$                              | 20   |         | 20  |      | ns    |

| A. Charle        | LOW                                               |                            | 20                                              |      | 20      |     |      |       |

| t <sub>pw</sub>  | Clock                                             | HIGH                       |                                                 | 20   |         | 20  |      | ns    |

| ts               | Data                                              |                            |                                                 | 15   |         | 15  |      | ns    |

| th               | Data                                              |                            |                                                 | 10   |         | 10  |      | ns    |

| te               | Data Enable                                       |                            |                                                 | 25   |         | 25  |      | ns    |

| th               | Data Enable                                       |                            |                                                 | 0    |         | 0   |      | ns    |

| ts               | Set-up Time, Clear<br>Recovery (Inactive) to      | Clock                      |                                                 | 23   |         | 24  |      | ns    |

| <sup>t</sup> zH  | Output Enable to Wi                               | Output Enghie to Mr. ov V. |                                                 |      | 24      |     | 27   | ns    |

| t <sub>ZL</sub>  | Output Enable to W <sub>i</sub> or Y <sub>i</sub> |                            |                                                 |      | 29      |     | 35   | 118   |

| tHZ              | Output Enable to Wi                               | or Vi                      | C <sub>L</sub> = 5.0pF                          |      | 33      |     | 45   | ne    |

| t <sub>LZ</sub>  | Output Engine to W                                | OI II                      | R <sub>L</sub> = 2.0kΩ                          |      | 22      |     | 26   | ns    |

| fmax             | Maximum Clock Frequ                               | uency (Note 1)             | C <sub>L</sub> = 50pF<br>R <sub>L</sub> = 2.0kΩ | 30   |         | 25  |      | MHz   |

<sup>\*</sup>Switching Characteristics' performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9.