# **DN8667NS**

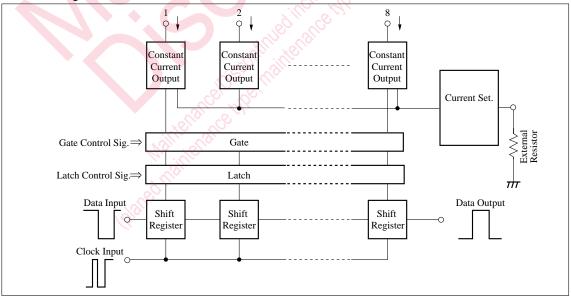

8-Bit Shift Register Latch Constant Current Driver IC

## Overview

The DN8667NS is a semiconductor integrated circuit which incorporates a 8-bit shift register, a latch driver and a constant current driver to satisfy the demand for equalization of LED panel brightness. It also incorporates the serial-in and serial-out/parallel-out functions. It employs the Bi-CMOS process : The 8-step shift register block and latch block consist of CMOS while the 8-step parallel driver block is bipolar.

## Features

- Serial-in, serial-out/parallel-out

- Cascade connection possible

- Constant current output (0 to 100 mA able to be set by one external resistor)

- Output-forced ON/OFF terminal attached (EN)

- Input/Output CMOS compatible

#### Application

LED panel drive

## Block Diagram

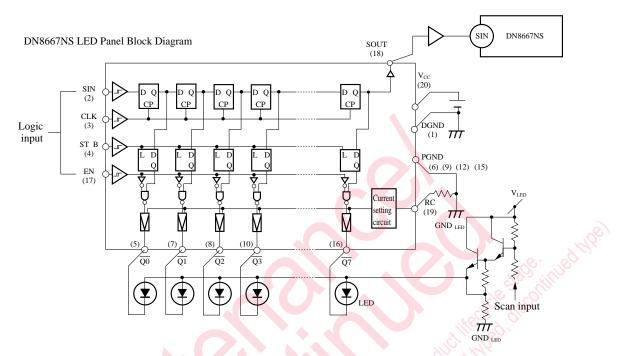

## DN8667NS

| Parameter                     | Symbol           | Rating       | Unit |

|-------------------------------|------------------|--------------|------|

| Supply voltage                | V <sub>CC</sub>  | 0 to + 7.0   | V    |

| Output voltage                | Vo               | 0 to + 14    | v    |

| Output current                | Io               | 150          | mA   |

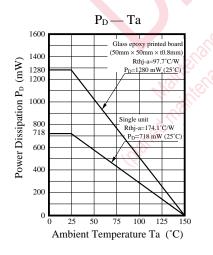

| Power dissipation*            | P <sub>D</sub>   | 1.28         | W    |

| Operating ambient temperature | T <sub>opr</sub> | -20 to + 85  | °C   |

| Storage temperature           | T <sub>stg</sub> | -55 to + 150 | °C   |

## Absolute Maximum Rating ( $Ta = 25^{\circ}C$ )

\* For printed board SM, it decreases with rate of 10.24 mW/°C from Ta = 25 °C.

## ■ Recommended Operation Range (Ta=25 °C)

| Parameter                | Symbol          | Range        |

|--------------------------|-----------------|--------------|

| Operating supply voltage | V <sub>CC</sub> | 4.5V to 5.5V |

## ■ Electrical Characteristics (V<sub>CC</sub>=5V,Ta=25±2°C)

| Parameter                          |                                    | Symbol           | Condition                                                                                                                                                  |                                   | min                   | typ                 | max          | Unit               |               |     |

|------------------------------------|------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|---------------------|--------------|--------------------|---------------|-----|

| Input voltage                      | Positive direction                 | V <sub>T+</sub>  | $ \begin{cases} V_{SOUT} = 0.1, V_{CC} - 0.1V \\  I_{SOUT}  = 20 \mu A \end{cases} $                                                                       |                                   |                       | 0.35V <sub>CC</sub> | —            | 0.7V <sub>cc</sub> | <u>fill</u> v |     |

| input vonage                       | Negative direction                 | V <sub>T-</sub>  | $ \left\{ \begin{array}{l} I_{O} \; (\overline{Qn}) = -10 \mu A, \; 90 m A \\ V_{O} \; (\overline{Qn}) = 0.6 V \; I_{ref} = -2.5 m A \end{array} \right. $ |                                   |                       | $0.2V_{\rm CC}$     | - CV         | 0.55Vcc            | v             |     |

| Input current                      | In mut our mont                    |                  | $V_{1H} = 5.0V$                                                                                                                                            |                                   |                       |                     | Coller &     | 25                 | μΑ            |     |

| input current                      |                                    | I <sub>IL</sub>  | $V_{1L} = 0V$                                                                                                                                              |                                   |                       | - 25                |              | —                  | μΑ            |     |

| Output voltage (SOUT)              |                                    | V <sub>OH</sub>  | $I_{OH} = -0.4 mA$                                                                                                                                         |                                   |                       | 4.0                 | Je star      |                    | V             |     |

|                                    | Output voltage (SOOT)              |                  | $I_{OL} = 1.6 mA$                                                                                                                                          |                                   |                       |                     | <u>13</u> 27 | 2                  | 0.5           | V   |

| Output current 1 $(\overline{Qn})$ | I <sub>OI</sub>                    | V <sub>o</sub> ( | $\overline{\mathbf{Qn}}$ ) = 0.                                                                                                                            | .5V                               | <u>(</u>              |                     |              | 100                | mA            |     |

| Output current 2 (Qn)              | Output current 2 $(\overline{Qn})$ |                  | $V_{\rm CC} = 5.0 \text{V}, I_{\rm ref} = -12 \text{mA}$                                                                                                   |                                   |                       | 83                  |              | 117                | mA            |     |

| Output current error betwee        | Output current error between bits  |                  | V <sub>o</sub> (                                                                                                                                           | $V_0(\overline{Qn}) = 1.0V$       |                       |                     | <u> </u>     |                    | ±6            | %   |

| Output leak current                | Output leak current                |                  |                                                                                                                                                            | V <sub>0</sub> = 14V (Output OFF) |                       |                     |              |                    | 25            | μΑ  |

|                                    |                                    | I <sub>CC1</sub> | OFF<br>Total Dr                                                                                                                                            |                                   | . 20                  | $I_{ref} = 0mA$     |              |                    | 2             | mA  |

| Supply current                     |                                    | I <sub>CC2</sub> | OFF ON<br>Total Driver Output                                                                                                                              | V <sub>cc</sub> =5                | .5V                   | $I_{ref} = -2.5 mA$ |              |                    | 20            | mA  |

|                                    |                                    | I <sub>CC3</sub> | NO                                                                                                                                                         | 2.112                             | R                     | $I_{ref} = -2.5 mA$ | —            | —                  | 30            | mA  |

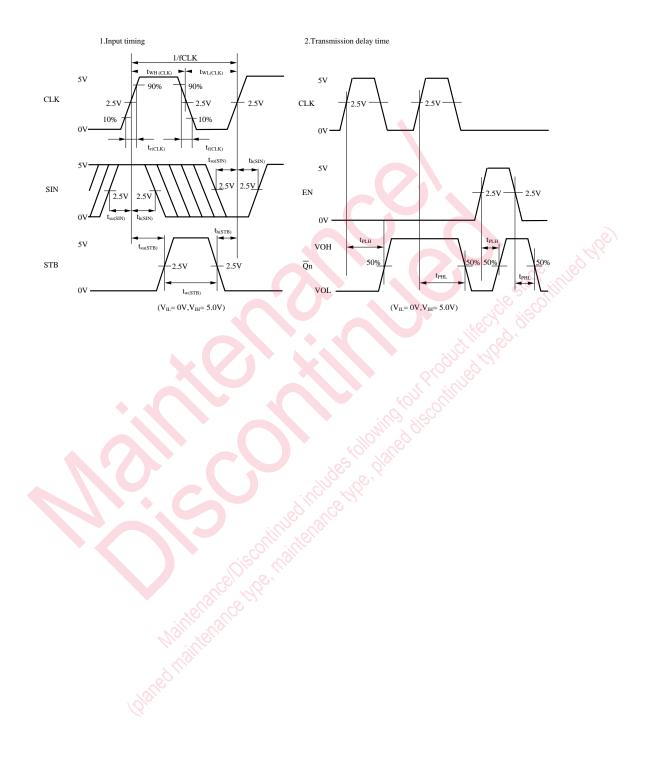

| Clock frequency                    |                                    | f <sub>CLK</sub> |                                                                                                                                                            | LK                                | Input                 | Duty 40 to 60%      |              | _                  | 20            | MHz |

| Input pulse width                  |                                    |                  | CLK                                                                                                                                                        |                                   |                       | 20                  |              |                    | ns            |     |

| input puise width                  |                                    | t <sub>w</sub>   | STB                                                                                                                                                        |                                   | V <sub>CC</sub> =5.0V |                     | 20           |                    |               | ns  |

| Setting-up time                    |                                    |                  | SIN                                                                                                                                                        |                                   | $R_1 = 50\Omega$      | 20                  |              |                    | ns            |     |

| Setting-up time                    |                                    | CEsu             | STB                                                                                                                                                        |                                   |                       | $C_L=15pF$          | 15           |                    |               | ns  |

| Halding time                       |                                    |                  | SIN<br>STB                                                                                                                                                 |                                   | ] `                   | CL-13PI             | 20           |                    |               | ns  |

| Holding time                       | inte                               | th               |                                                                                                                                                            |                                   |                       |                     | 10           |                    |               | ns  |

| Clock pulse rise time              | N.o. X                             | ک t <sub>r</sub> |                                                                                                                                                            |                                   |                       |                     |              |                    | 500           | ns  |

| Clock pulse fall time              | SI                                 | $t_{\rm f}$      |                                                                                                                                                            |                                   |                       |                     |              |                    | 500           | ns  |

Note)  $V_{CC}=5V$  unless otherwise specified.

## Others

## Pin Descriptions

| Pin No.                          | Symbol          | Pin name                       | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|----------------------------------|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1                                | DGND            | Digital ground                 | Digital ground                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 2                                | SIN             | Serial data input              | It is the serial data input terminal for shift register.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 3                                | CLK             | Clock input                    | The value of shift register shifts at the rising edge of clock input.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 4                                | STB             | Strobe input                   | Setting the STB input to "H" forwards the data of shift register to the latch.<br>When the STB input is set to "L", even if the value of shift register changes,<br>the value of latch is not changed.                                                                                                                                                                                                |  |  |  |  |  |

| 5<br>7,8<br>10,11<br>13,14<br>16 | $\overline{Qn}$ | Driver output                  | It outputs signals by using the polarity opposite to that of data taken into the latch. For example, when the value of serial input is "H", the output becomes "L" level and the output is turned on. The output takes open collector form of NPN transistor.                                                                                                                                         |  |  |  |  |  |

| 6<br>9,12<br>15                  | PGND            | Output ground                  | Output ground                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 17                               | EN              | Enabling input                 | When the EN input is set to "H", all the outputs are turned off, independent of condition of shift register or latch driver.                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 18                               | SOUT            | Serial data output             | It is the terminal which performs the serial-output of data inputted from the SIN.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 19                               | RC              | Constant current setting input | It connects the external resistor between RC and GND and sets the current of output block.<br>* Output current calculation : ** RC terminal setting calculation :<br>$I_{O}(\overline{Qn}) \approx \frac{20 \times V_{CC}(V)}{R_{RC}(\Omega) + 90}$ $I_{RC} \approx \frac{V_{CC}(V)}{2 \times R_{RC}(\Omega) + 180}$ or $R_{RC} \approx \frac{1}{2} \left( \frac{V_{CC}(V)}{I_{RC}(A)} - 180 \right)$ |  |  |  |  |  |

| 20                               | V <sub>CC</sub> | V <sub>cc</sub>                | Supply terminal                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

\* Calculation example  $V_{CC} = 5V$   $R_{RC} = 910\Omega$   $R_{RC} \approx 100$   $I_0(\overline{Qn}) \approx \frac{20 \times 5}{910 + 90}$   $I_0(\overline{Qn}) \approx 100$  M \*\* Calculation example  $R_{RC} \approx \frac{1}{2} \left(\frac{5}{0.0025} - 180\right)$   $I_{RC} \approx 0.0025A$  $R_{RC} \approx 910 (\Omega)$

Panasonic

## Application Circuit

## ■ Function Table (Note)

| Input        |     |    |     | Output           |                      |                  |                |  |

|--------------|-----|----|-----|------------------|----------------------|------------------|----------------|--|

| CLK          | STB | EN | SIN | $\overline{Q_0}$ | $\overline{Q_m}$     | $\overline{Q_7}$ | SOUT           |  |

| $\uparrow$   | Н   | L  | Qn  | $\overline{Q_n}$ | $\overline{Q_{m-1}}$ | $\overline{Q_6}$ | Q <sub>6</sub> |  |

| $\uparrow$   | L   | L  | Qn  | nc               | nc                   | nc               | Q <sub>6</sub> |  |

| $\uparrow$   | ×   | Н  | Qn  | Н                | Н                    | Н                | Q <sub>6</sub> |  |

| $\downarrow$ | ×   | ×  | Qn  | nc               | nc                   | nc               | nc             |  |

#### (Note) H : High level, L: Low level, × : H or L $Q_m, Q_n : H \text{ or } L.$ However, for $Q_{n_n}$ "H"= OFF, "L"= ON. $\uparrow$ : Shift from L to H, $\downarrow$ : Shift from H to L

nc : No change

Characteristics Curve

## Timing Chart

## Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure

- mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.