# ML65F16241

# 16-Bit Buffer/Line Driver with 3-State Outputs

#### GENERAL DESCRIPTION

The ML65F16241 is a BiCMOS, 16-bit buffer/line driver with 3-state outputs. This device was specifically designed for high speed bus applications. Its 16 channels support propagation delay of 2ns maximum, and fast output enable and disable times of 5ns or less to minimize datapath delay.

This device is designed to minimize undershoot, overshoot, and ground bounce to decrease noise delays. These transceivers implement a unique digital and analog implementation to eliminate the delays and noise inherent in traditional digital designs. The device offers a new method for quickly charging up a bus load capacitor to minimize bus settling times, or FastBus™ Charge. FastBus Charge is a transition current, (specified as IDYNAMIC) that injects between 60 to 200mA (depending on output load) of current during the rise time and fall time. This current is used to reduce the amount of time it takes to charge up a heavily-capacitive loaded bus, effectively reducing the bus settling times, and improving data/clock margins in tight timing budgets.

Micro Linear's solution is intended for applications for critical bus timing designs that include minimizing device propagation delay, bus settling time, and time delays due to noise. Applications include; high speed memory arrays, bus or backplane isolation, bus to bus bridging, and sub-2ns propagation delay schemes.

The ML65F16241 follows the pinout and functionality of the industry standard 2.7V to 3.6V-logic families.

#### **FEATURES**

- Low propagation delays 2ns maximum for 3.3V, 2.5ns maximum for 2.7V

- Fast output enable/disable times of 5ns maximum

- FastBus Charge current to minimize the bus settling time during active capacitive loading

- 2.7V to 3.6V V<sub>CC</sub> supply operation; LV-TTL compatible input and output levels with 3-state capability

- Industry standard pinout compatible to FCT, ALV, LCX, LVT, and other low voltage logic families

- ESD protection exceeds 2000V

- Full output swing for increased noise margin

- Undershoot and overshoot protection to 400mV typically

- Low ground bounce design

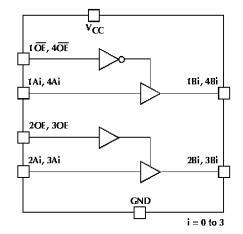

#### **BLOCK DIAGRAM**

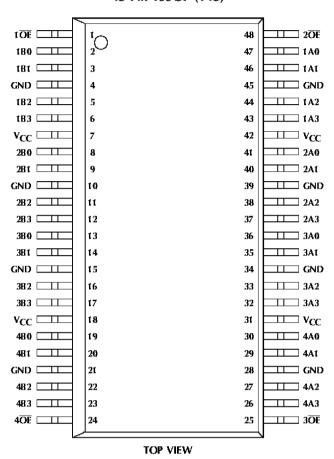

## PIN CONFIGURATION

ML65F16241 48-Pin SSOP (R48) 48-Pin TSSOP (T48)

## **FUNCTION TABLE**

(Each 4-bit section)

| INP                                          | OUTPUTS |           |

|----------------------------------------------|---------|-----------|

| 1 <del>OE</del> , 4 <del>OE</del> 1 Ai, 4 Ai |         | 1 Bi, 4Bi |

| L                                            | Н       | н         |

| L                                            | L       | L         |

| Н                                            | X       | Z         |

| INP      | OUTPUTS           |   |

|----------|-------------------|---|

| 2OE, 3OE | 2OE, 3OE 2Ai, 3Ai |   |

| Н        | Н                 | Н |

| Н        | L                 | L |

| L        | Χ                 | Z |

L = Logic Low, H = Logic High, X = Don't Care, Z = High Impedance

i = 0 to 3

# PIN DESCRIPTION

| PIN | NAME             | FUNCTION                 | PIN | NAME            | FUNCTION                  |

|-----|------------------|--------------------------|-----|-----------------|---------------------------|

| 1   | 1 <del>OE</del>  | Output Enable Active Low | 25  | 3OE             | Output Enable Active High |

| 2   | 1B0              | Data Output              | 26  | 4A3             | Data Input                |

| 3   | 1B1              | Data Output              | 27  | 4A2             | Data Input                |

| 4   | GND              | Signal Ground            | 28  | GND             | Signal Ground             |

| 5   | 1B2              | Data Output              | 29  | 4 <b>A</b> 1    | Data Input                |

| 6   | 1B3              | Data Output              | 30  | 4A0             | Data Input                |

| 7   | V <sub>CC</sub>  | 2.7V to 3.6V Supply      | 31  | V <sub>CC</sub> | 2.7V to 3.6V Supply       |

| 8   | 2B0              | Data Output              | 32  | 3A3             | Data Input                |

| 9   | 2B1              | Data Output              | 33  | 3A2             | Data Input                |

| 10  | GND              | Signal Ground            | 34  | GND             | Signal Ground             |

| 11  | 2B2              | Data Output              | 35  | 3A1             | Data Input                |

| 12  | 2B3              | Data Output              | 36  | 3A0             | Data Input                |

| 13  | 3B0              | Data Output              | 37  | 2A3             | Data Input                |

| 14  | 3B1              | Data Output              | 38  | 2A2             | Data Input                |

| 15  | GND              | Signal Ground            | 39  | GND             | Signal Ground             |

| 16  | 3B2              | Data Output              | 40  | 2A1             | Data Input                |

| 17  | 3B3              | Data Output              | 41  | 2A0             | Data Input                |

| 18  | $V_{CC}$         | 2.7V to 3.6V Supply      | 42  | $V_{CC}$        | 2.7V to 3.6V Supply       |

| 19  | 4B0              | Data Output              | 43  | 1A3             | Data Input                |

| 20  | 4B1              | Data Output              | 44  | 1A2             | Data Input                |

| 21  | GND              | Signal Ground            | 45  | GND             | Signal Ground             |

| 22  | 4B2              | Data Output              | 46  | 1A1             | Data Input                |

| 23  | 4B3              | Data Output              | 47  | 1A0             | Data Input                |

| 24  | 4 <del>O</del> E | Output Enable Active Low | 48  | 2OE             | Output Enable Active High |

|     |                  |                          |     |                 |                           |

## ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| V <sub>CC</sub>                     | 7V           |

|-------------------------------------|--------------|

| DC Input Voltage                    |              |

| AC Input Voltage (PW < 20ns)        | 3.0V         |

| DC Output Voltage                   | 0.3V to 7VDC |

| Output Current, Source or Sink (AC) |              |

| Storage Temperature Range           | -65°C to 150°C |

|-------------------------------------|----------------|

| Junction Temperature                |                |

| Lead Temperature (Soldering, 10sec) |                |

| Thermal Impedance (θιΔ)             |                |

#### **OPERATING CONDITIONS**

| Temperature Range               | 0°C to  | 70°C |

|---------------------------------|---------|------|

| V <sub>IN</sub> Operating Range | 2.7V to | 3.6V |

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $V_{IN} = 3.3V$ ,  $T_A = Operating Temperature Range (Note 1).$

| SYMBOL                              | PARAMETER                                      | CONDITIONS                                              | CONDITIONS                    |      | TYP  | MAX  | UNITS |

|-------------------------------------|------------------------------------------------|---------------------------------------------------------|-------------------------------|------|------|------|-------|

| AC ELECTE                           | RICAL CHARACTERISTICS (C <sub>LOAD</sub> = 50p | F)                                                      | '                             |      |      | •    |       |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay                              | Ai to Bi                                                | 3.3V                          | 1.35 | 1.7  | 2    | ns    |

|                                     |                                                |                                                         | 2.7V                          | 1.25 | 1.9  | 2.5  | ns    |

| t <sub>OE</sub>                     | Output Enable Time                             | OE to Ai/Bi                                             | 3.3V                          |      |      | 5    | ns    |

|                                     |                                                |                                                         | 2.7V                          |      |      | 6    | ns    |

|                                     |                                                | DIR to Ai/Bi                                            | 3.3V                          |      |      | 5    | ns    |

|                                     |                                                |                                                         | 2.7V                          |      |      | 6    | ns    |

| t <sub>OD</sub>                     | Output Disable Time                            | OE to Ai/Bi                                             | 3.3V                          |      |      | 5    | ns    |

|                                     |                                                |                                                         | 2.7V                          |      |      | 6    | ns    |

|                                     |                                                | DIR to Ai/Bi                                            | 3.3V                          |      |      | 5    | ns    |

|                                     |                                                |                                                         | 2.7V                          |      |      | 6    | ns    |

| Tos                                 | Output-to-Output Skew                          |                                                         |                               |      |      | 300  | ps    |

| C <sub>IN</sub>                     | Input Capacitance                              |                                                         |                               |      |      | 5    | pF    |

| DC ELECTI                           | RICAL CHARACTERISTICS (C <sub>LOAD</sub> = 50p | F, R <sub>LOAD</sub> = Open)                            |                               |      |      |      |       |

| V <sub>IH</sub>                     | Input High Voltage                             | Logic high                                              |                               | 2.0  |      |      | V     |

| V <sub>IL</sub>                     | Input Low Voltage                              | Logic low                                               |                               |      |      | 0.8  | V     |

| ΙΗ                                  | Input High Current                             | Per pin, V <sub>IN</sub> = 3V                           | Per pin, V <sub>IN</sub> = 3V |      |      | 300  | mA    |

| I <sub>IL</sub>                     | Input Low Current                              | Per pin, V <sub>IN</sub> = 0V                           |                               |      |      | 300  | mA    |

| I <sub>HI-Z</sub>                   | Three-State Output Current                     | $V_{CC} = 3.6V, 0 < V_{IN} < V_{CC}$                    | 0                             |      |      | 5    | mA    |

| V <sub>IC</sub>                     | Input Clamp Voltage                            | $V_{CC} = 3.6V$ , $I_{IN} = 18mA$                       |                               |      | -0.7 | -0.2 | V     |

| I <sub>DYNAMIC</sub>                | Dynamic Transition Current<br>(FastBus Charge) | Low to high transitions                                 | Low to high transitions       |      | 80   |      | mA    |

|                                     |                                                | High to low transitions                                 |                               |      | 80   |      | mA    |

| V <sub>OH</sub>                     | Output High Voltage                            | V <sub>C</sub>                                          | <sub>CC</sub> = 3.6V          | 2.4  | 3.4  |      | ٧     |

|                                     |                                                | Vo                                                      | <sub>CC</sub> = 2.7V          | 2.25 | 2.35 |      | V     |

| V <sub>OL</sub>                     | Output LowVoltage                              | V <sub>CC</sub> = 2.7V and 3.6V                         |                               |      |      | 0.6  | V     |

| Icc                                 | Quiescent Power Supply Current                 | $V_{CC} = 3.6V$ , $f = 0Hz$ , Inputs = $V_{CC}$ or $0V$ |                               |      |      | 3    | μA    |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

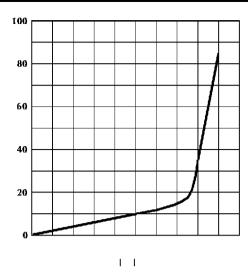

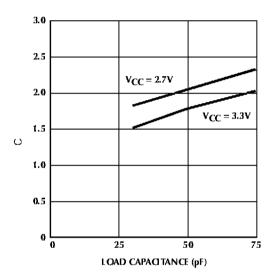

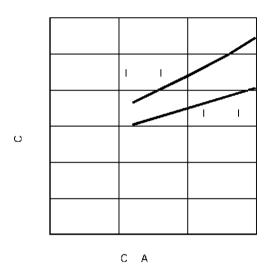

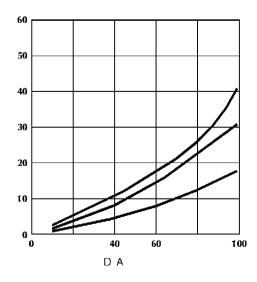

Figure 1a. Typical  $V_{OL}$  vs.  $I_{OL}$  for 3.3V  $V_{CC}$ . One Buffer Output

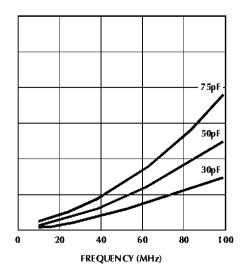

Figure 2a. Propagation Delay vs. Load Capacitance: 3.3V, 50MHZ

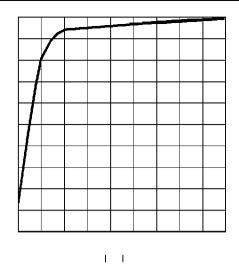

Figure 3a.  $I_{CC}$  vs. Frequency:  $V_{CC} = V_{IN} = 3.3V$ . One Buffer Output

Figure 1b. Typical  $V_{OH}$  vs.  $I_{OH}$  for 3.3V  $V_{CC}$ . One Buffer Output

Figure 2b. Propagation Delay vs. Load Capacitance: 2.7 V, 50MHZ

Figure 3b.  $I_{CC}$  vs. Frequency:  $V_{CC} = V_{IN} = 2.7V$ . One Buffer Output

# **FUNCTIONAL DESCRIPTION**

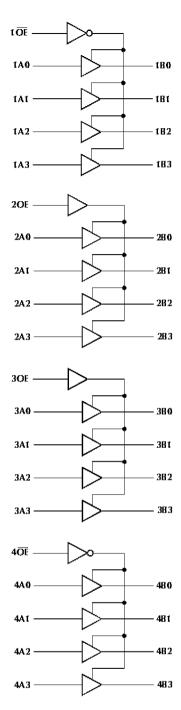

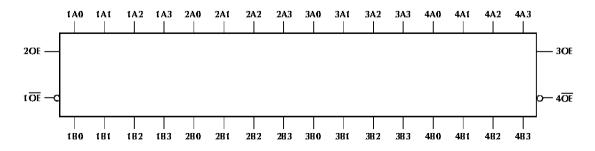

Figure 4. Logic Diagram

Figure 5. Logic Symbol

#### ARCHITECTURAL DESCRIPTION

The ML65F16241 is a 16-bit buffer/line driver with 3-state outputs designed for 2.7V to 3.6V  $V_{CC}$  operation. This device is designed for Quad-Nibble, Dual-Byte memory interleaving operations. Each bank has an independently controlled 3-state output enable pin with output enable/disable access times of less than 7ns. Each bank is configured to have four independent buffer/line drivers. Two banks are active high enabled and the other two banks are active low enabled. Thus making this device ideal for nibble or byte swapping operations in cache or main memory designs by toggling between the active low and active high output enable pins.

Until now, these transceivers were typically implemented in CMOS logic and made to be TTL compatible by sizing the input devices appropriately. In order to buffer large capacitances with CMOS logic, it is necessary to cascade an even number of inverters, each successive inverter larger than the preceding, eventually leading to an inverter that will drive the required load capacitance at the required frequency. Each inverter stage represents an additional delay in the gating process because in order for a single gate to switch, the input must slew more than half of the supply voltage. The best of these 16-bit CMOS buffers has managed to drive 50pF load capacitance with a delay of 3ns.

Micro Linear has produced a 16-bit buffer/line driver with a delay less than 2ns (3.3V) by using a unique circuit architecture that does not require cascade logic gates.

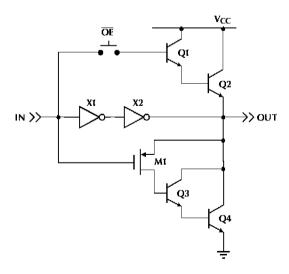

The basic architecture of the ML65F16241 is shown in Figure 6. In this circuit, there are two paths to the output. One path sources current to the load capacitance where the signal is asserted, and the other path sinks current from the output when the signal is negated.

The assertion path is the Darlington pair consisting of transistors Q1 and Q2. The effect of transistor Q1 is to increase the current gain through the stage from input to output, to increase the input resistance and to reduce input capacitance. During an input low-to-high transition, the output transistor Q2 sources large amount of current to quickly charge up a highly capacitive load which in effect reduces the bus settling time. This current is specified as IDYNAMIC.

The negation path is also the Darlington pair consisting of transistor Q3 and transistor Q4. With M1 connecting to the input of the Darlington pair, Transistor Q4 then sinks a large amount of current during the input transition from high-to-low.

Inverter X2 is a helpful buffer that not only drives the output toward the upper rail but also pulls the output to the lower rail.

Figure 6. One Buffer Cell of the ML65F16241

## **CIRCUITS AND WAVE FORMS**

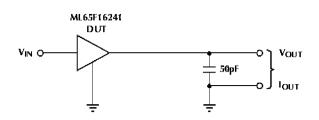

Figure 7. Test Circuits for All Outputs

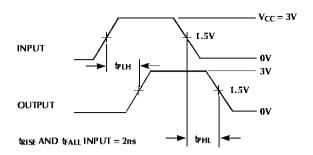

Figure 8. Propagation Delay

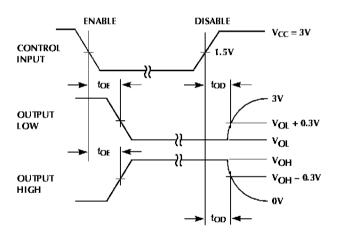

Figure 9. Enable and Disable Times

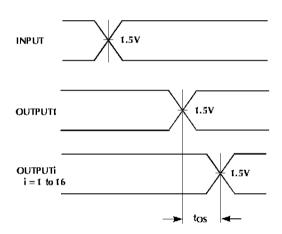

Figure 10. Output Skew

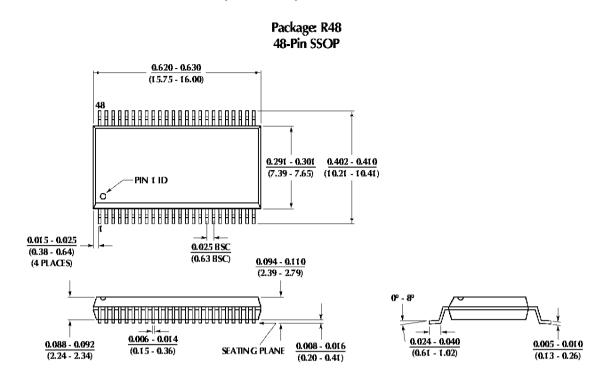

# PHYSICAL DIMENSIONS inches (millimeters)

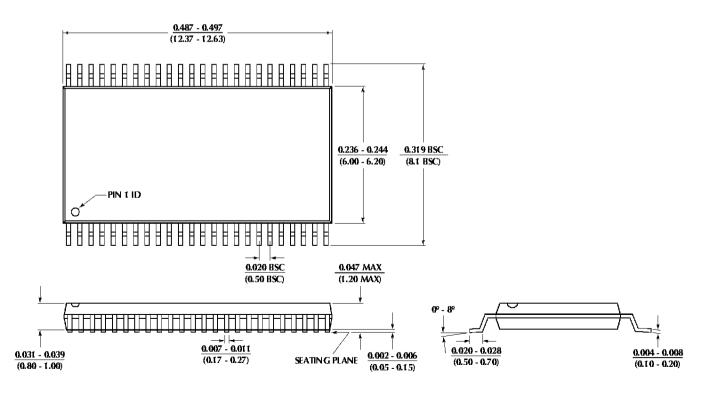

#### Package: T48 48-Pin TSSOP

#### ORDERING INFORMATION

| PART NUMBER  | TEMPERATURE RANGE | PACKAGE            |  |  |

|--------------|-------------------|--------------------|--|--|

| ML65F16241CR | 0°C to 70°C       | 48-Pin SSOP (R48)  |  |  |

| ML65F16241CT | 0°C to 70°C       | 48-Pin TSSOP (T48) |  |  |

Discretinear 1998. All Micro Linear is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; Japan: 2,598,946; 2,619,299; 2,704,176. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right northerights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: (408) 433-5200 Fax: (408) 432-0295 www.microlinear.com

To receive a price quote or to request a product sample, call or send e-mail to your local representative.

When sending e-mail, be sure to include the Micro Linear part number and whether you want a price quote or a sample in the subject line.

(i.e. subject: Sample request - ML part#xxxx)

Click here to find your local representative