# PM-155A/PM-156A/PM-157A

MONOLITHIC JFET-INPUT OPERATIONAL AMPLIFIERS

## Precision Monolithics Inc.

LOW SUPPLY CURRENT — PM-155A/PM-355A/PM-155 GENERAL PURPOSE — PM-156A/PM-356A/PM-156 WIDE-BANDWIDTH — PM-157A/PM-357A/PM-157

## **FEATURES**

## All Devices

| • | Low Input Bias and Offset Currents                           |  |  |  |  |  |  |  |

|---|--------------------------------------------------------------|--|--|--|--|--|--|--|

| • | Low Input Offset Voltage 1.0mV                               |  |  |  |  |  |  |  |

| • | Low Input Offset Voltage Drift 3.0 μV/° C                    |  |  |  |  |  |  |  |

| • | Low Input Noise Current 0.01pA/ $\sqrt{\text{Hz}}$           |  |  |  |  |  |  |  |

| • |                                                              |  |  |  |  |  |  |  |

|   | PM-155 (Only) LF155 Replacement                              |  |  |  |  |  |  |  |

| • | Low Supply Current 2mA                                       |  |  |  |  |  |  |  |

|   | PM-156 (Only) LF156 Replacement                              |  |  |  |  |  |  |  |

| • | High Slew Rate 12V/μsec                                      |  |  |  |  |  |  |  |

|   | Fast Settling to $\pm 0.01\%$ 4.0 $\mu$ sec                  |  |  |  |  |  |  |  |

|   | PM-157 (Only) LF157 Replacement                              |  |  |  |  |  |  |  |

| • | Wide-Bandwidth Decompensated (A <sub>VCI</sub> = 5 Min)20MHz |  |  |  |  |  |  |  |

| • | High Slew Rate 45V/μsec                                      |  |  |  |  |  |  |  |

| • | Fast Settling to ± 0.01% 4.0 usec                            |  |  |  |  |  |  |  |

# **GENERAL DESCRIPTION**

The PM JFET-input series provides low input current, high slew rate, and direct interchangeability with LF155, 156, and 157 types. These operational amplifiers use a new process which allows fabrication of matched JFET transistors and standard bipolar transistors on the same chip. High accuracy and low cost make the PM JFET-input series useful in new designs and as replacements for modular and hybrid types. Unlike many designs, nulling the input offset voltage does not degrade common-mode rejection ratio or input offset voltage drift. Low input voltage noise and current noise plus a low 1/f noise corner frequency allow these amplifiers to be used in a variety of low noise, wide-bandwidth applications.

Dynamic specifications for the PM-155 include a slew rate of  $5V/\mu s$ , a 2.5MHz gain bandwidth product, and settling time to within  $\pm 0.01\%$  of final value in  $5.0\mu s$ . The PM-156 has a slew rate of  $12V/\mu s$  and a settling time of  $4.0\mu s$  to  $\pm 0.01\%$  of final value.

The PM-157 is a very fast decompensated device. This results in a  $45V/\mu s$  slew rate, a 20MHz gain bandwidth product, and a settling time of  $4.0\mu s$ . Decompensation requires a minimum closed-loop gain of five because of stability considerations.

For improved performance, see the OP-15/OP-16/OP-17 data sheet. For duals, see the OP-215 data sheet.

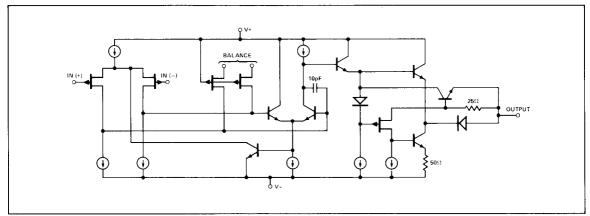

# SIMPLIFIED SCHEMATIC

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage<br>PM-155A, PM-156A, PM-157A, PM-155, PM-156, PM-157,<br>PM-355A, PM-356A, PM-357A |

|---------------------------------------------------------------------------------------------------|

| Operating Temperature Range                                                                       |

| PM-155A, PM-156A, PM-157A, PM-155, PM-156,                                                        |

| PM-15755° C to +125° C                                                                            |

| PM-355A, PM-356A, PM-357A 0°C to +70°C                                                            |

| Maximum Junction Temperature (T <sub>i</sub> )                                                    |

| PM-155A, PM-156A, PM-157A, PM-155, PM-156,                                                        |

| PM-157 + 150° C                                                                                   |

| PM-355A, PM-356A, PM-357A+100° C                                                                  |

| Differential Input Voltage                                                                        |

| PM-155A, PM-156A, PM-157A, PM-155, PM-156, PM-157,                                                |

| PM-355A, PM-356A, PM-357A ±40V                                                                    |

| Input Voltage                                                                                     |

| PM-155A, PM-156A, PM-157A, PM-155, PM-156, PM-157,                                                |

PM-355A, PM-356A, PM-357A ..... ±20V

| Output Short-Circuit Duration              | Indefinite |

|--------------------------------------------|------------|

| Storage Temperature Range65° C             | to +150° C |

| Lead Temperature Range (Soldering, 60 sec) | . +300°C   |

| PACKAGE TYPE           | Θ <sub>JA</sub> (NOTE 2) | Θ <sub>j¢</sub> | UNITS |

|------------------------|--------------------------|-----------------|-------|

| TO-99 (J)              | 150                      | 18              | °C/W  |

| 8-Pin Hermetic DIP (Z) | 148                      | 16              | °C/W  |

| 20-Contact LCC (RC)    | 98                       | 38              | °C/W  |

## NOTES:

- The absolute maximum negative input voltage is equal to the negative power supply voltage.

- Θ<sub>|A</sub> is specified for worst case mounting conditions, i.e., Θ<sub>|A</sub> is specified for device in socket for TO, CerDIP, and LCC packages.

**ELECTRICAL CHARACTERISTICS** at  $\pm$ 15V  $\leq$  V<sub>S</sub>  $\leq$   $\pm$ 20V, -55° C  $\leq$  T<sub>A</sub>  $\leq$  +125° C and T<sub>HIGH</sub> = +125° C for PM-155A, PM-156A and PM-157A, 0° C  $\leq$  T<sub>A</sub>  $\leq$  +70° C and T<sub>HIGH</sub> = +70° C for PM-355A, PM-356A and PM-357A, unless otherwise noted.

|                                                             | :                                                    |                                                                           | P            | PM-155A/<br>PM-156A/<br>PM-157A |     | PM-355A/<br>PM-356A/<br>PM-357A |                 |     |              |

|-------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|--------------|---------------------------------|-----|---------------------------------|-----------------|-----|--------------|

| PARAMETER                                                   | SYMBOL                                               | CONDITIONS                                                                | MIN          | TYP                             | MAX | MIN                             | TYP             | MAX | UNITS        |

| Input Offset Voltage                                        | V <sub>os</sub>                                      | $R_S = 50\Omega$                                                          | _            | 1.4                             | 2.5 |                                 | 1.2             | 2.3 | mV           |

| Input Offset Voltage Drift                                  | TCVOS                                                | $R_S = 50\Omega$                                                          | _            | 3                               | 5   |                                 | 3               | 5   | μV/° C       |

| Change in Input Offset<br>Drift with V <sub>OS</sub> Adjust | $\left(\frac{\Delta TCV_{OS}}{\Delta V_{OS}}\right)$ | $R_S = 50\Omega$                                                          | _            | 0.5                             |     | -                               | 0.5             | _   | μV/°C per mV |

| Input Offset Current                                        | los                                                  | T <sub>j</sub> ≤ T <sub>HIGH</sub> (Note 1)                               | _            | 4.0                             | 10  |                                 | 0.4             | 1.0 | nA           |

| Input Bias Current                                          | I <sub>B</sub>                                       | T <sub>J</sub> ≤ T <sub>HIGH</sub> · Note 1 ·                             | _            | ± 10                            | ±25 | _                               | ±2              | ±5  | nA           |

| Large-Signal Voltage Gain                                   | A <sub>vo</sub>                                      | $V_S = \pm 15V, V_O = \pm 10V,$<br>$R_L = 2k\Omega$                       | 25           | 75                              | _   | 25                              | 75              | _   | V/mV         |

| Output Voltage Swing                                        | v <sub>o</sub>                                       | $V_S = \pm 15V$ , $R_L = 10k\Omega$<br>$V_S = \pm 15V$ , $R_L = 2k\Omega$ | ± 12<br>± 10 | ± 13<br>± 12                    | _   | ± 12<br>± 10                    | ± 13<br>± 12    | _   | v            |

| Input Voltage Range                                         | IVR                                                  | V <sub>S</sub> = ± 15V                                                    | ±10.4        | + 15.1<br>-12.0                 | _   | ±10.4                           | + 15.1<br>-12.0 | _   | V            |

| Common-Mode Rejection<br>Ratio                              | CMRR                                                 | V <sub>CM</sub> = ± IVR                                                   | 85           | 100                             | _   | 85                              | 100             | _   | dB           |

| Power Supply Rejection<br>Ratio                             | PSRR                                                 | (Note 2)                                                                  |              | 10                              | 57  |                                 | 10              | 57  | μV/V         |

## NOTES:

- 1. PMI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps.  $I_B$  and  $I_{OS}$  are measured at  $V_{CM} = 0$ .

- Power supply rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously, in accordance with common practice.

|                           |                 |                                                                     |                            | Pi        | M-155<br>M-156<br>M-157 | Ã/          | P           | M-355<br>M-356<br>M-357 | A/            |            |

|---------------------------|-----------------|---------------------------------------------------------------------|----------------------------|-----------|-------------------------|-------------|-------------|-------------------------|---------------|------------|

| PARAMETER                 | SYMBOL          | CONDITIONS                                                          |                            | MIN       | TYP                     | MAX         | MIN         | TYP                     | MAX           | UNITS      |

| Input Offset Voltage      | v <sub>os</sub> | R <sub>S</sub> = 50Ω                                                |                            | _         | 1                       | 2           | _           | 1                       | 2             | mV         |

| Input Offset Current      | Ios             | T <sub>j</sub> = 25° C (Note 1)                                     |                            | _         | 3                       | 10          | _           | 3                       | 10            | рA         |

| Input Bias Current        | I <sub>B</sub>  | T <sub>j</sub> = 25° C (Note 1)                                     |                            | _         | ±30                     | ±50         | _           | ±30                     | ±50           | pA         |

| Input Resistance          | R <sub>IN</sub> |                                                                     |                            | _         | 10 <sup>12</sup>        | _           | _           | 10 <sup>12</sup>        | _             | n          |

| Large-Signal Voltage Gain | A <sub>vo</sub> | $V_S = \pm 15V, V_O = \pm 10V,$<br>$R_L = 2k\Omega$                 |                            | 50        | 200                     | _           | 50          | 200                     | -             | V/mV       |

| Supply Current            | Isy             | V <sub>S</sub> = ± 15V                                              | PM-155<br>PM-156/PM-157    | _         | 2<br>5                  | 4<br>7      | _           | 2                       | <b>4</b><br>7 | mA         |

| Slew Rate                 | SR              | $A_{VCL} = +1, V_S = \pm 15V$                                       | PM-155<br>PM-156           | 3<br>10   | 5<br>12                 | _           | 3<br>10     | 5<br>12                 | _             | V/μs       |

| ·····                     |                 | $A_{VCL} = +5, V_S = \pm 15V$                                       | PM-157                     | 40        | 45                      | -           | 40          | 45                      |               |            |

| Gain Bandwidth Product    | GBW             | $A_{VCL} = +1, V_S = \pm 15V$<br>$A_{VCL} = +5, V_S = \pm 15V$      | PM-155<br>PM-156<br>PM-157 | 4.0<br>15 | 2.5<br>4.5<br>20        | -<br>-<br>- | 4.0<br>15   | 2.5<br>4.5<br>20        | _             | MHz        |

| Settling Time (to ±0.01%) | t <sub>S</sub>  | V <sub>S</sub> = ±15V (Note 2)                                      | PM-155<br>PM-156           |           | 5.0<br>4.0              |             | _<br>_<br>_ | 4.0<br>1.5              | _             | μs         |

| 15 1.1 1                  |                 | V <sub>S</sub> = ± 15V (Note 3)                                     | PM-157                     | _         | 4.0                     | _           |             | 1.5                     |               |            |

| Input Noise Voltage       | e <sub>n</sub>  | $R_S = 100\Omega$ , $f = 100Hz$<br>$R_S = 100\Omega$ , $f = 1000Hz$ | PM-155                     | _         | 25<br>20                | _           | _           | 25<br>20                | _             | nV/√Hz     |

| mps. Holse voltage        | ™<br>           | $R_S = 100\Omega$ , $f = 100Hz$<br>$R_S = 100\Omega$ , $f = 1000Hz$ | PM-156/PM-157              | _         | 15<br>12                |             |             | 15<br>12                |               | 1147 V 112 |

| Input Noise Current       | in              | $f = 100$ Hz, $V_S = \pm 15$ V<br>$f = 1000$ Hz, $V_S = \pm 15$ V   |                            | _         | 0.01<br>0.01            | _           | _           | 0.01<br>0.01            | _             | pA∕√Hz     |

| Input Capacitance         | C <sub>IN</sub> |                                                                     |                            | _         | 3                       | _           | _           | 3                       | _             | pF         |

# NOTES:

PMI)

- 1. PMI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps.  $I_B$  and  $I_{OS}$  are measured at  $V_{CM} = 0$ .

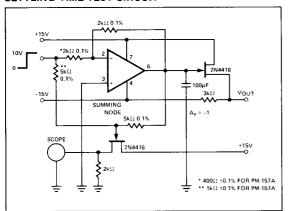

- Settling time is defined here for a unity gain inverter connection using 2kΩ resistors. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 10V step input is applied to the inverter. See settling time test circuit.

- 3. Settling time is defined here for a  $A_V = -5$  connection with  $R_F = 2k\Omega$ . It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 2V step input is applied to the inverter. See settling time test circuit.

# **ELECTRICAL CHARACTERISTICS** at $T_A = +25^{\circ}$ C, $\pm 15$ V $\leq$ V<sub>S</sub> $\leq \pm 20$ V for PM-155, PM-156 and PM-157, unless otherwise noted.

|                           |                 |                                                                                                        |                            |             | PM-155<br>PM-156<br>PM-157 |               |                             |

|---------------------------|-----------------|--------------------------------------------------------------------------------------------------------|----------------------------|-------------|----------------------------|---------------|-----------------------------|

| PARAMETER                 | SYMBOL          | CONDITIONS                                                                                             |                            | MIN         | TYP                        | MAX           | UNITS                       |

| Input Offset Voltage      | V <sub>OS</sub> | $R_S = 50\Omega$                                                                                       |                            |             | 3                          | 5             | mV                          |

| Input Offset Current      | Ios             | T <sub>j</sub> = 25° C (Note 1)                                                                        |                            | _           | 3                          | 20            | рА                          |

| Input Bias Current        | I <sub>B</sub>  | T <sub>j</sub> = 25° C (Note 1)                                                                        |                            |             | ±30                        | ± 100         | pA                          |

| Input Resistance          | R <sub>IN</sub> |                                                                                                        |                            |             | 10 <sup>12</sup>           |               | Ω                           |

| Large-Signal Voltage Gain | A <sub>VO</sub> | $V_{S} = \pm 15V, V_{O} = \pm 10V,$ $R_{L} = 2k\Omega$                                                 |                            | 50          | 200                        | -             | V/mV                        |

| Supply Current            | I <sub>SY</sub> | $V_S = \pm 15V$                                                                                        | PM-155<br>PM-156/PM-157    | _           | 2 5                        | 4             | mA                          |

| Slew Rate                 | SR              | $A_{VCL} = +1, V_S = \pm 15V$<br>$A_{VCL} = +5, V_S = \pm 15V$                                         | PM-155<br>PM-156<br>PM-157 | 7.5<br>30   | 5<br>12<br>40              | _<br>_<br>_   | V/µs                        |

| Gain Bandwidth Product    | ĠВŴ             | $A_{VCL} = +1$ , $V_S = \pm 15V$<br>$A_{VCL} = +5$ , $V_S = \pm 15V$                                   | PM-155<br>PM-156<br>PM-157 | _           | 2.5<br>5<br>20             | _<br>_<br>_   | MHz                         |

| Settling Time (to ±0.01%) | t <sub>S</sub>  | $V_S = \pm 15V \text{ (Note 2)}$<br>$V_S = \pm 15V \text{ (Note 3)}$                                   | PM-155<br>PM-156<br>PM-157 | _           | 5<br>4<br>4                |               | μς                          |

| Input Noise Voltage       | e <sub>n</sub>  | $R_S = 100\Omega$ , $f = 100Hz$<br>$R_S = 100\Omega$ , $f = 1000Hz$<br>$R_S = 100\Omega$ , $f = 100Hz$ | PM-155                     | _<br>_<br>_ | 25<br>20<br>15             | <u>-</u><br>- | nV/√Hz                      |

| Input Noise Current       | in              | $R_S = 100\Omega$ , $f = 1000Hz$<br>$f = 100Hz$ , $V_S = \pm 15V$<br>$f = 1000Hz$ , $V_S = \pm 15V$    | E MI-130/ E MI-137         |             | 0.01                       | _             | p <b>A</b> /√ <del>Hz</del> |

| Input Capacitance         | C <sub>IN</sub> |                                                                                                        |                            |             | 3                          | _             | pF                          |

# NOTES:

- 1. PMI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps. I  $_{B}$  and I  $_{OS}$  are measured at  $_{CM}=0$ .

- 2. Settling time is defined here for a unity gain inverter connection using  $2k\Omega$  resistors. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 10V step input is applied to the inverter. See settling time test circuit.

- 3. Settling time is defined here for a  $A_V$ = -5 connection with  $R_F$ =  $2k\Omega$ . It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 2V step input is applied to the inverter. See settling time test circuit.

**ELECTRICAL CHARACTERISTICS** at  $\pm$  15V  $\leq$  V<sub>S</sub> $\leq$   $\pm$  20V and -55° C  $\leq$  T<sub>A</sub> $\leq$  + 125° C and T<sub>HIGH</sub>= + 125° C for PM-155, PM-156 and PM-157, unless otherwise noted.

|                                                              |                                                      |                                                                           |              | PM-155<br>PM-156<br>PM-157 |          | , , , , , , , , , , , , , , , , , , , , |

|--------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|--------------|----------------------------|----------|-----------------------------------------|

| PARAMETER                                                    | SYMBOL                                               | CONDITIONS                                                                | MIN          | TYP                        | MAX      | UNITS                                   |

| Input Offset Voltage                                         | V <sub>OS</sub>                                      | $R_S = 50\Omega$                                                          | _            | 4                          | 7        | mV                                      |

| Input Offset Voltage<br>Drift                                | TCVos                                                | $R_S = 50\Omega$                                                          |              | 5                          | _        | μV/° C                                  |

| Change In Input Offset<br>Drift With V <sub>OS</sub> Adjust. | $\left(\frac{\Delta TCV_{OS}}{\Delta V_{OS}}\right)$ | $R_S = 50\Omega$                                                          | _            | 0.5                        |          | μV/°C<br>per mV                         |

| Input Offset Current                                         | los                                                  | T <sub>j</sub> ≤ T <sub>HIGH</sub> (Note 1)                               |              | 8                          | 20       | nA                                      |

| Input Bias Current                                           | I <sub>B</sub>                                       | T <sub>j</sub> ≤ T <sub>HIGH</sub> (Note 1)                               | <del>-</del> | ±2                         | ±50      | nA                                      |

| Large-Signal Voltage<br>Gain                                 | Avo                                                  | $V_S = \pm 15V$ , $V_O = \pm 10V$<br>$R_L = 2k\Omega$                     | 25           | 75                         | _        | V/mV                                    |

| Output Voltage Swing                                         | v <sub>o</sub>                                       | $V_S = \pm 15V$ , $R_L = 10k\Omega$<br>$V_S = \pm 15V$ , $R_L = 2k\Omega$ | ± 12<br>± 10 | ± 13<br>± 12               | <u>-</u> | v                                       |

| Input Voltage Range                                          | IVR                                                  | V <sub>S</sub> = ± 15V                                                    | ±10.4        | + 15.1<br>- 12.0           | _        | V                                       |

| Common-Mode<br>Rejection Ratio                               | CMRR                                                 | V <sub>CM</sub> = ± IVR                                                   | 85           | 100                        | _        | dB                                      |

| Power Supply<br>Rejection Ratio                              | PSRR                                                 | (Note 2)                                                                  | _            | 10                         | 57       | μV/V                                    |

#### NOTES:

PMI)

- 1. PMI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps. IB and IOS are measured at  $V_{CM} = 0$ ,  $T_j = +125$ ° C.

- 2. Power supply rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously, in accordance with common practice.

# ORDERING INFORMATION<sup>†</sup>

|                                                       |                | PACKAGE     |                                   |     |

|-------------------------------------------------------|----------------|-------------|-----------------------------------|-----|

| T <sub>A</sub> = 25° C<br>V <sub>OS</sub> MAX<br>(mV) | TO-99<br>8-PIN | LCC         | OPERATING<br>TEMPERATURE<br>RANGE |     |

|                                                       | PM155AJ*       | PM155AZ/883 | PM155ARC/883                      |     |

| 2.0                                                   | PM156AJ*       | PM156AZ*    | PM156ARC/883                      | MIL |

|                                                       | PM157AJ/883    | PM157AZ*    |                                   |     |

|                                                       | PM355AJ        | PM355AZ     | _                                 |     |

| 2.0                                                   | PM356AJ        | PM356AZ     | _                                 | COM |

|                                                       | PM357AJ        | PM357AZ     | -                                 |     |

|                                                       | PM155J*        | PM155Z*     | _                                 |     |

| 5.0                                                   | PM156J*        | PM156Z*     | _                                 | MIL |

|                                                       | PM157J*        | PM157Z*     | _                                 |     |

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages. For ordering information, see 1990/91 Data Book, Section 2.

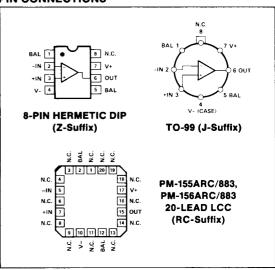

# **PIN CONNECTIONS**

#### **BASIC CONNECTIONS**

## SETTLING-TIME TEST CIRCUIT

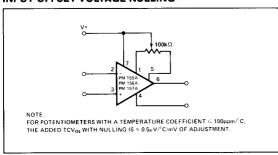

#### INPUT OFFSET VOLTAGE NULLING

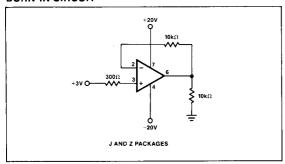

## **BURN-IN CIRCUIT**

# **APPLICATIONS INFORMATION**

# INPUT VOLTAGE CONSIDERATIONS

The PM series JFET input stages can accommodate large input differential voltages without external clamping as long as neither input exceeds the negative power supply. An input voltage which is more negative than V- can result in a destroyed unit.

If both inputs exceed the negative common-mode voltage limit, the amplifier will be forced to a high positive output. If only one input exceeds the negative common-mode voltage limit, a phase reversal takes place forcing the output to the corresponding high or low state. In either of the above conditions, normal operation will return when both inputs are returned to within the specified common-mode voltage range.

Exceeding the positive common-mode limit on a single input will not change the phase of the output. However, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

# POWER SUPPLY CONSIDERATIONS

Power supply polarity reversal can result in a destroyed unit.

# **DYNAMIC OPERATING CONSIDERATIONS**

As with most amplifiers, care should be taken with lead dress, component placement, and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input. This minimizes "pick-up" and increases the frequency of the feedback pole by minimizing the capacitance from input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device to AC ground sets the frequency of the pole. In many instances, the frequency of this pole is much greater than the expected 3dB frequency of the closed-loop gain. Consequently, the pole has negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3dB frequency, a lead capacitor should be placed from the output to the inverting input of the op amp. The capacitor value should be such that the RC time constant of the capacitor and feedback resistor is greater than, or equal to, the original feedback-pole time constant.