### SN54AS821A, SN74AS821A 10-BIT BUS-INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS

SDAS230A - DECEMBER 1983 - REVISED AUGUST 1995

- Functionally Equivalent to AMD's AM29821

- Provide Extra Data Width Necessary for Wider Address/Data Paths or Buses With Parity

- Outputs Have Undershoot-Protection Circuitry

- Power-Up High-Impedance State

- Buffered Control Inputs to Reduce dc Loading Effects

- Package Options Include Plastic Small-Outline (DW) Packages, Ceramic Chip Carriers (FK), and Standard Plastic (NT) and Ceramic (JT) 300-mil DIPs

#### description

These 10-bit flip-flops feature 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing wider buffer registers, I/O ports, bidirectional bus drivers with parity, and working registers.

The ten flip-flops are edge-triggered D-type flip-flops. On the positive transition of the clock (CLK) input, the Q outputs are true to the data (D) input.

A buffered output-enable ( $\overline{OE}$ ) input can be used to place the ten outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive bus lines without interface or pullup components.

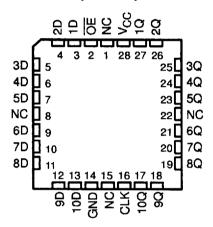

SN54AS821A ... JT PACKAGE SN74AS821A ... DW OR NT PACKAGE (TOP VIEW)

SN54AS821A ... FK PACKAGE (TOP VIEW)

NC - No internal connection

OE does not affect the internal operation of the flip-flops. Previously stored data can be retained or new data can be entered while the outputs are in the high-impedance state.

The SN54AS821A is characterized for operation over the full military temperature range of –55°C to 125°C. The SN74AS821A is characterized for operation from 0°C to 70°C.

# FUNCTION TABLE (each flip-flop)

|    | INPUTS     |   | OUTPUT |

|----|------------|---|--------|

| ŌE | CLK        | D | Q      |

| L  | 1          | Н | Н      |

| L  | $\uparrow$ | L | L      |

| L  | L          | Х | $Q_0$  |

| Н  | Х          | Χ | z      |

PRODUCTION DATA Information is current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1995, Texas instruments Incorporated

SDAS230A - DECEMBER 1983 - REVISED AUGUST 1995

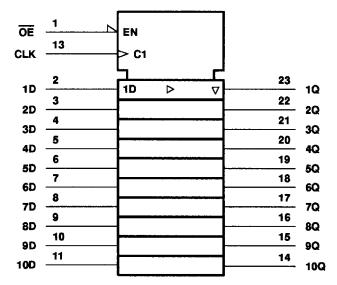

#### logic symbol†

† This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the DW, JT, and NT packages.

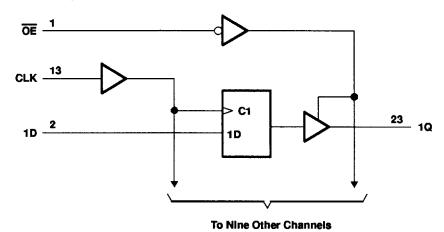

#### logic diagram (positive logic)

Pin numbers shown are for the DW, JT, and NT packages.

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| Supply voltage, V <sub>CC</sub>                      | 7 V            |

|------------------------------------------------------|----------------|

| Input voltage, V <sub>I</sub>                        | 7 V            |

| Voltage applied to a disabled 3-state output         | 5.5 V          |

| Operating free-air temperature range, TA: SN54AS821A | -55°C to 125°C |

| SN74AS821A                                           | 0°C to 70°C    |

| Storage temperature range                            | -65°C to 150°C |

<sup>‡</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SDAS230A - DECEMBER 1983 - REVISED AUGUST 1995

## recommended operating conditions

|                   |                                 | SN  | SN54AS821A |     |     | SN74AS821A |     |      |

|-------------------|---------------------------------|-----|------------|-----|-----|------------|-----|------|

|                   |                                 | MIN | NOM        | MAX | MIN | NOM        | MAX | UNIT |

| VCC               | Supply voltage                  | 4.5 | 5          | 5.5 | 4.5 | 5          | 5.5 | ٧    |

| ۷ıH               | High-level input voltage        | 2   |            |     | 2   |            |     | ٧    |

| VIL               | Low-level input voltage         |     |            | 0.8 |     |            | 0.8 | V    |

| Юн                | High-level output current       |     |            | -24 |     |            | -24 | mA   |

| lOL               | Low-level output current        |     |            | 32  |     |            | 48  | mA   |

| t <sub>w</sub> *  | Pulse duration, CLK high or low | 9   |            |     | 8   |            |     | ns   |

| t <sub>su</sub> * | Setup time, data before CLK?    | 7   |            |     | 6   |            |     | ns   |

| th*               | Hold time, data after CLK↑      | 0   |            |     | 0   |            |     | ns   |

| TA                | Operating free-air temperature  | -55 |            | 125 | 0   |            | 70  | °C   |

<sup>\*</sup> On products compliant to MIL-STD-883, Class B, this parameter is based on characterization data but is not production tested.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         | TEST CONDITIONS                             |                         | SN54AS821A         |      |      | SN74AS821A |      |      |      |

|-------------------|---------------------------------------------|-------------------------|--------------------|------|------|------------|------|------|------|

|                   |                                             |                         | MIN                | TYP† | MAX  | MIN        | TYPT | MAX  | UNIT |

| ٧ <sub>IK</sub>   | $V_{CC} = 4.5 V$ ,                          | i <sub>l</sub> = -18 mA |                    |      | ~1.2 |            |      | -1.2 | ٧    |

|                   | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$ | I <sub>OH</sub> = -2 mA | V <sub>CC</sub> -2 |      |      | VCC -2     | 2    |      | -    |

| VOH               | V <sub>CC</sub> = 4.5 V                     | IOH = -15 mA            | 2.4                | 3.2  |      | 2.4        | 3.2  |      | ٧    |

|                   |                                             | IOH = -24 mA            | 2                  |      |      | 2          |      |      |      |

| V <sub>OL</sub> V | V <sub>CC</sub> = 4.5 V                     | I <sub>OL</sub> = 32 mA |                    | 0.25 | 0.5  |            |      |      | ٧    |

| •OL               | VCC = 4.5 V                                 | I <sub>OL</sub> = 48 mA |                    |      |      |            | 0.35 | 0.5  |      |

| <sup>I</sup> OZH  | V <sub>CC</sub> = 5.5 V,                    | V <sub>O</sub> = 2.7 V  |                    |      | 50   |            |      | 50   | μΑ   |

| <sup>l</sup> OZL  | V <sub>CC</sub> = 5.5 V,                    | V <sub>1</sub> = 0.4 V  |                    |      | -50  |            |      | -50  | μΑ   |

| - II              | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 7 V    |                    |      | 0.1  |            |      | 0.1  | mΑ   |

| l <sub>IH</sub>   | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 2.7 V  |                    |      | 20   |            |      | 20   | μΑ   |

| اړړ               | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 0.4 V  |                    |      | -0.5 |            |      | -0.5 | mA   |

| 1O <sup>‡</sup>   | V <sub>CC</sub> = 5.5 V,                    | V <sub>O</sub> = 2.25 V | -30                |      | -112 | -30        |      | -112 | mA   |

| lcc               | V <sub>CC</sub> = 5.5 V                     | Outputs high            |                    | 55   | 88   |            | 55   | 88   | -    |

|                   |                                             | Outputs low             |                    | 68   | 109  |            | 68   | 109  |      |

|                   |                                             | Outputs disabled        |                    | 70   | 113  |            | 70   | 113  |      |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

<sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

# SN54AS821A, SN74AS821A 10-BIT BUS-INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS SDAS230A - DECEMBER 1983 - REVISED AUGUST 1995

## switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | то<br>(О <b>บ</b> тр <b>и</b> т) | V <sub>C</sub><br>C <sub>L</sub><br>R1<br>R2<br>T <sub>A</sub> | UNIT  |            |     |    |

|------------------|-----------------|----------------------------------|----------------------------------------------------------------|-------|------------|-----|----|

|                  |                 |                                  | SN54A                                                          | S821A | SN74AS821A |     |    |

|                  |                 |                                  | MIN                                                            | MAX   | MIN        | MAX |    |

| t <sub>PLH</sub> | CLK             | Any Q                            | 3.5                                                            | 9     | 3.5        | 7.5 | ns |

| tPHL             |                 |                                  | 3.5                                                            | 14    | 3.5        | 13  |    |

| <sup>†</sup> PZH | ŌĒ<br>·         | Апу Q                            | 4                                                              | 12    | 3          | 11  |    |

| t <sub>PZL</sub> |                 |                                  | 4                                                              | 13    | 4          | 12  | ns |

| <sup>t</sup> PHZ | ŌĒ              | A O                              | 1                                                              | 10    | 1          | 8   |    |

| <sup>t</sup> PLZ |                 | Any Q                            | 1                                                              | 10    | 1          | 8   | ns |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

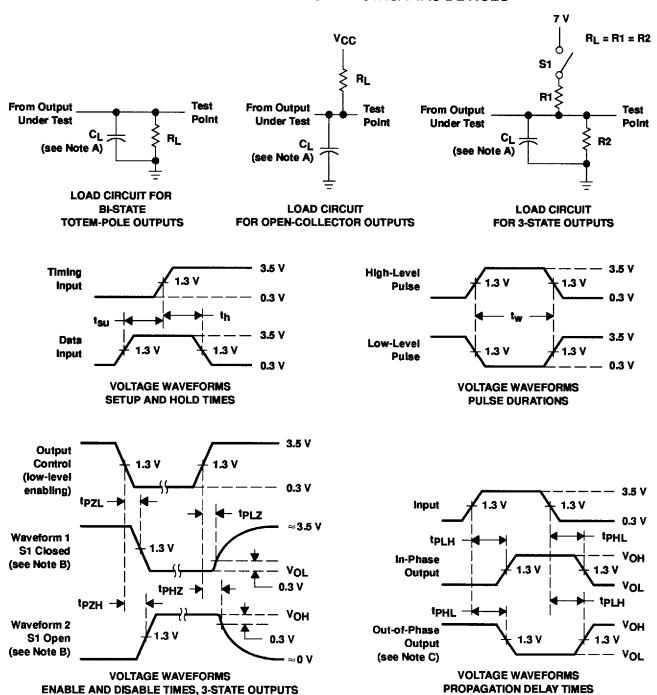

# PARAMETER MEASUREMENT INFORMATION SERIES 54ALS/74ALS AND 54AS/74AS DEVICES

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

- D. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_r = t_f = 2$  ns, duty cycle = 50%.

- E. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms