#### TARGET SPECIFICATIONS

PI5B32861

# 3.3V, 10-Bit, 2-Port Bus Switch with $25\Omega$ Series Resistor

#### **Product Features:**

- Near zero propagation delay

- $5\Omega$  switches with  $25\Omega$  series resistor connect inputs to outputs

- Direct bus connection when switches are ON

- Ultra Low Quiescent Power (0.2 µA Typical)

- Ideally suited for notebook applications

- Packages available:

- 24-pin 150 mil wide plastic QSOP (Q24)

# **Product Description:**

Pericom Semiconductor's PI5C series of logic circuits are produced in the Company's advanced 0.35 micron CMOS technology, achieving industry leading performance.

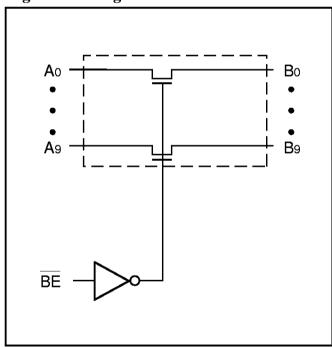

The PI5C32861 is a 3.3 Volt, 10-bit, 2-port bus switch designed with a low ON resistance that permits inputs to be connected directly to outputs. The bus switch creates no additional propagational delay or additional ground bounce noise. The switches are turned ON by the Bus Enable (BE) input signal. The PI5B32861 is designed with an internal  $25\Omega$  resistor that reduces noise reflection in high speed applications

# Logic Block Diagram

## **Product Pin Configuration**

| NC =         | 1 O          | 24      |

|--------------|--------------|---------|

| A1 🗀         | 3            | 22 Bo   |

| A2 🗀         | 4            | 21 🏳 B1 |

| A3 🗀         | 5            | 20 🖂 B2 |

| A4 🗀         | 6 24-PIN     | 19 🗀 B3 |

| <b>A</b> 5 □ | 7 <b>Q24</b> | 18 🗀 B4 |

| A6 🗀         | 8            | 17 🗀 B5 |

| <b>A</b> 7 □ | 9            | 16 🗀 B6 |

| A8 🗀         | 10           | 15 🗀 B7 |

| A9 🗀         | 11           | 14 🗀 B8 |

| GND □        | 12           | 13 🖂 B9 |

|              |              |         |

# **Product Pin Description**

1

| Pin Name           | Description                   |

|--------------------|-------------------------------|

| $\overline{ m BE}$ | Bus Enable Input (Active LOW) |

| A0–9               | Bus A                         |

| B0-9               | Bus B                         |

| GND                | Ground                        |

| Vcc                | Power                         |

# Truth Table<sup>(1)</sup>

| Function   | $\overline{\mathbf{BE}}$ | A0-9 |

|------------|--------------------------|------|

| Disconnect | Н                        | Hi-Z |

| Connect    | L                        | B0-9 |

Note:

1. H = High Voltage Level L = Low Voltage Level

Hi-Z = High Impedance

PS8154 11/17/97

## TARGET SPECIFICATIONS

F15632801

F15632801

3.3V, 10-BIT, 2-PORT BUS SWITCH

WITH 25Ω SERIES RESISTOR

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                                    |

|----------------------------------------------------------------------|

| Ambient Temperature with Power Applied40°C to +85°C                  |

| Supply Voltage to Ground Potential (Inputs & Vcc Only)0.5V to +4.6V  |

| Supply Voltage to Ground Potential (Outputs & D/O Only)0.5V to +4.6V |

| DC Input Voltage0.5V to +4.6V                                        |

| DC Output Current                                                    |

| Power Dissipation                                                    |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **DC Electrical Characteristics** (Over the Operating Range, TA = -40°C to +85°C, $VCC = 5V \pm 5\%$ )

| Parameters | Description                         | Test Conditions(1)                                                                  | Min.     | $\mathbf{Typ}^{(2)}$ | Max.     | Units |

|------------|-------------------------------------|-------------------------------------------------------------------------------------|----------|----------------------|----------|-------|

| VIH        | Input HIGH Voltage                  | Guaranteed Logic HIGH Level                                                         | 2.0      |                      |          | V     |

| VIL        | Input LOW Voltage                   | Guaranteed Logic LOW Level                                                          | -0.5     |                      | 0.8      | V     |

| Im         | Input HIGH Current                  | Vcc = Max., Vin = Vcc                                                               |          |                      | ±50      | μA    |

| IIL        | Input LOW Current                   | Vcc = Max., Vin = GND                                                               |          |                      | ±50      | μA    |

| Iozh       | High Impedance Output Current       | 0 - A, B - Vcc                                                                      |          |                      | ±1       | μA    |

| VIK        | Clamp Diode Voltage                 | Vcc = Min., Iin = -18 mA                                                            |          |                      | -0.8     | V     |

| Ron        | Switch On Resistance <sup>(4)</sup> | Vcc = Min., Vin = 0.0V, Ion = 48 mA or 64 mA<br>Vcc = Min., Vin = 2.4V, Ion = 15 mA | 18<br>18 | 28<br>35             | 40<br>48 | Ω     |

#### Capacitance ( $T_A = 25^{\circ}C$ , f = 1 MHz)

| Parameters(5) | Description                 | Test Conditions     | Тур | Units |

|---------------|-----------------------------|---------------------|-----|-------|

| Cin           | Input Capacitance           | $V_{IN} = 0V$       | 4   | pF    |

| Coff          | A/B Capacitance, Switch Off | V <sub>IN</sub> =0V | 4   | pF    |

| Сон           | A/B Capacitance, Switch On  | Vin=0V              | 8   | pF    |

## Notes:

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 3.3V, TA = 25°C ambient and maximum loading.

- 3. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

- 4. Measured by the voltage drop between A and B pin at indicated current through the switch. ON resistance is determined by the lower of the voltages on the two (A,B) pins.

2

5. This parameter is determined by device characterization but is not production tested.

PS8154 11/17/97

## **Power Supply Characteristics**

| Parameters | Description                            | Test Conditions <sup>(1)</sup> |                       | Min. | <b>Typ</b> <sup>(2)</sup> | Max. | Units |

|------------|----------------------------------------|--------------------------------|-----------------------|------|---------------------------|------|-------|

| Icc        | Quiescent Power<br>Supply Current      | Vcc = Max.                     | VIN = GNDorVcc        |      | 0.1                       | 3.0  | μА    |

| ΔΙcc       | Supply Current per<br>Input @ TTL HIGH | Vcc = Max.                     | $V_{IN} = 3.0V^{(3)}$ |      |                           | 750  | μА    |

#### Notes:

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device.

- 2. Typical values are at Vcc = 3.3V, +25°C ambient.

- 3. Per TTL driven input (VIN = 3.0V, control inputs only); A and B pins do not contribute to Icc.

- 4. This current applies to the control inputs only and represent the current required to switch internal capacitance at the specified frequency. The A and B inputs generate no significant AC or DC currents as they transition. This parameter is not tested, but is guaranteed by design.

# **Switching Characteristics over Operating Range**

|                                                        |                                                       |                                            | PI5B32861 |      |      |

|--------------------------------------------------------|-------------------------------------------------------|--------------------------------------------|-----------|------|------|

|                                                        |                                                       |                                            | Com.      |      |      |

| Parameters                                             | Description                                           | Conditions(2,3)                            | Max       | Min  | Unit |

| t <sub>PLH</sub><br>t <sub>PHL</sub>                   | Propagation Delay <sup>(2,3)</sup> Ax to Bx, Bx to Ax | $C_{L} = 50 \text{ pF}, R_{L} = 500\Omega$ |           | 1.25 |      |

| t <sub>ezh</sub>                                       | Bus Enable Time                                       | $C_{L} = 20 \text{ pF}, R_{L} = 500\Omega$ | 1         | 2    |      |

| t <sub>pzz</sub>                                       |                                                       | $C_{L} = 50 \text{ pF}, R_{L} = 500\Omega$ | 1         | 3.5  | ns   |

| $t_{PHZ}$ Bus Disable Time $\overline{BE}$ to Ax or Bx | $C_{L} = 20 \text{ pF}, R_{L} = 500\Omega$            | 1                                          | 2         |      |      |

|                                                        | $C_{L} = 50 \text{ pF}, R_{L} = 500\Omega$            | 1                                          | 4.0       |      |      |

#### Notes:

- 1. See test circuit and waveforms.

- 2. This parameter is guaranteed but not tested on Propagation Delays.

- 3. The bus switch contributes no propagational delay other than the RC delay of the ON resistance of the switch and the load capacitance. The time constant for the switch alone is of the order of 1.25ns for 50 pF load. Since this time constant is much smaller than the rise/fall times of typical driving signals, it adds very little propagational delay to the system. Propagational delay of the bus switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side.

3